October 1990

# Datasheet.Suppor

# Interfacing Intel 82596 LAN Coprocessors with M68000 Family Microprocessors

Some portions of this document were provided by Dr. Design of San Diego, CA

Order Number: 292076-001

#### 1

# Interfacing Intel 82596 LAN Coprocessors with M68000 Family Microprocessors

| CONTENTS PAGE                            | CONTENTS                     | PAGE           |

|------------------------------------------|------------------------------|----------------|

| <b>1.0 INTRODUCTION</b> 1-497            | 4.0 M68000/82596DX INTERFAC  | <b>E</b> 1-509 |

| 1.1 Scope 1-497                          | 4.1 Design Specifications    | 1-509          |

| 1.2 Fundamental Assumptions 1-497        | 4.2 Clocking                 | 1-509          |

| 2.0 GENERIC IMPLEMENTATION ISSUES1-497   | 4.3 Reset Timing             |                |

| 2.1 Block Definitions 1-497              | 4.5 Bus Arbiter              |                |

| 2.2 Clocking 1-499                       | 4.6 Memory Signal Conversion |                |

| 2.3 Reset Retiming 1-499                 | 4.7 Wait State Generator     |                |

| 2.4 CA and PORT Generation 1-500         | 5.0 MC68000/82596SX INTERFA  | CF 1-511       |

| 2.5 Arbitration 1-501                    | 5.1 Design Specifications    |                |

| 2.5.1 Refresh Requests 1-501             | 5.2 Clocking                 |                |

| 2.5.2 82596 Requests 1-501               | 5.3 Reset Retiming           |                |

| 2.5.3 Arbiter Implementation 1-502       | 5.4 CA and PORT Generator    |                |

| 2.6 Signal Conversion 1-504              | 5.5 Bus Arbiter              |                |

| 2.7 Wait State and Burst Generator 1-505 | 5.6 Memory Signal Conversion |                |

| 2.7.1 General Information 1-505          | 5.7 Wait State Generator     |                |

| 2.7.2 Single Cycle Bus Transfers         | APPENDIX A SCHEMATICS        | 1-514          |

| 2.7.3 Burst-Cycle and Multiple-          | A.1 MC68030/82596CA          | 1-515          |

| Cycle Bus Transfers 1-505                | A.2 MC68020/82596DX          | 1-516          |

| 3.0 MC68030/82596CA INTERFACE 1-506      | A.3 MC68000/82596SX          | 1-517          |

| 3.1 Design Specifications 1-506          | APPENDIX B PLD EQUATIONS     | 1-518          |

| 3.2 Clocking 1-506                       | B.1 MC68030/82596CA          | 1-519          |

| 3.3 Reset Retiming 1-506                 | B.2 MC68020/82596DX          | 1-530          |

| 3.4 CA and PORT Generator 1-506          | B.3 MC68000/82596SX          | 1-539          |

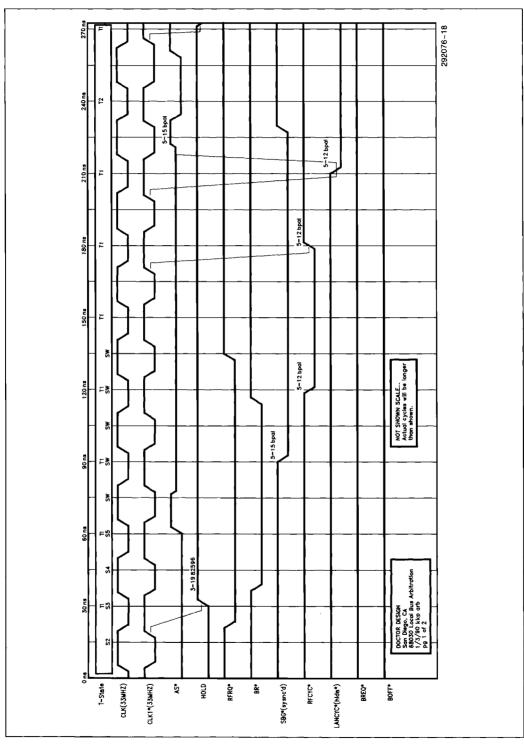

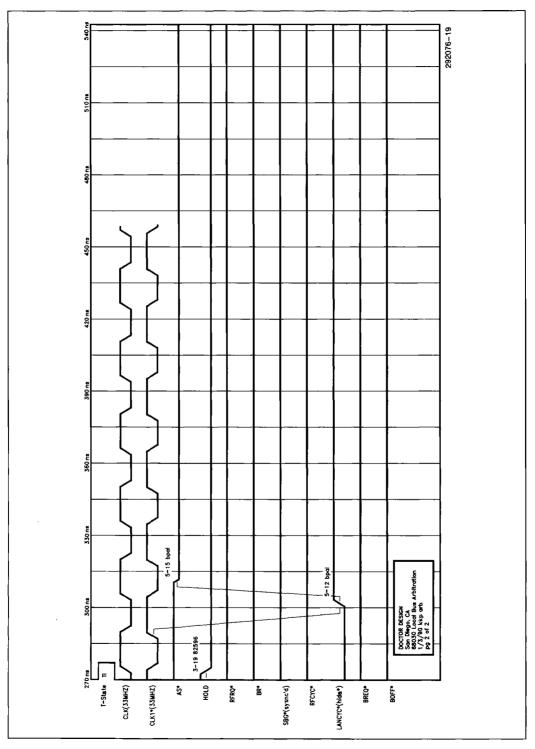

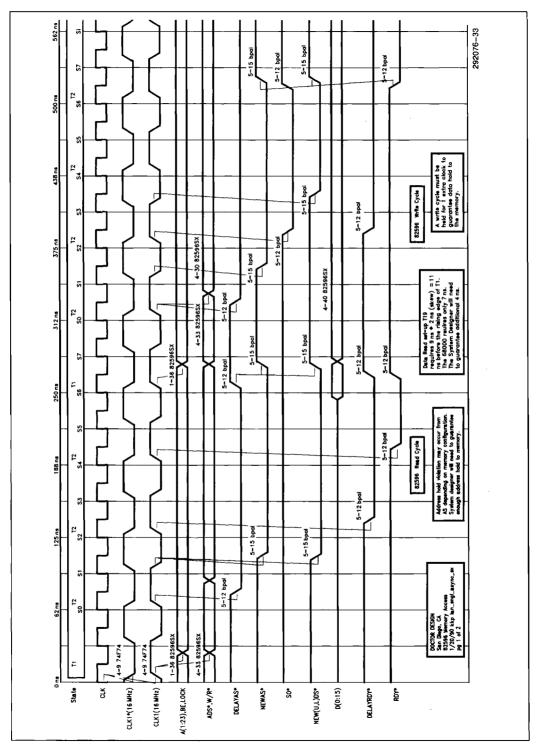

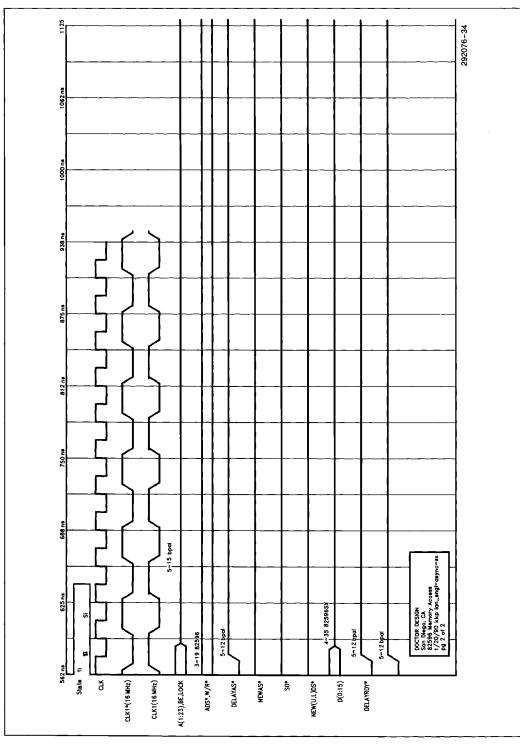

| 3.5 Bus Arbiter                          | APPENDIX C TIMING DIAGRAMS   | S 1.545        |

| 3.6 Memory Signal Conversion 1-507       | C.1 MC68030/82596CA          |                |

| 3.7 Wait State and Burst Generator 1-508 | C.2 MC68020/82596DX          |                |

| 3.7.1 General Information 1-508          | C.3 MC68000/82596SX          |                |

| 3.7.2 Single Cycle Transfers 1-508       |                              |                |

| 3.7.3 Burst Cycle Bus Transfers 1-508    | APPENDIX D PARTS LIST        | 1-569          |

Throughout this document, M68000 is used as a general reference to a family of microprocessors, which includes the MC68000, MC68020, MC68030. A reference to a particular member of the family will use the MC prefix followed by the specific number. 82596 is used as a general reference to a family of LAN coprocessors—the 82596CA, 82596DX, and 82596SX. A reference to a particular member of the family will use 82596 followed by the two letter suffix.

## **Table of Figures and Tables**

| CONTE     | ENTS                                                           | PAGE    |

|-----------|----------------------------------------------------------------|---------|

| FIGURES   | <b>S</b>                                                       |         |

| Figure 1  | M68000 Family and 82596 Family Interface Generic Block Diagram | . 1-498 |

| Figure 2  | Clock Timing Relationships                                     | . 1-498 |

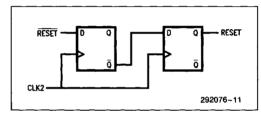

| Figure 3  | Reset Retiming Block Diagram                                   | . 1-499 |

| Figure 4  | CA and PORT Block Diagram                                      | . 1-500 |

| Figure 5  | CA and PORT State Transition Diagram                           | . 1-500 |

| Figure 6  | Arbiter State Transition Diagram                               | . 1-503 |

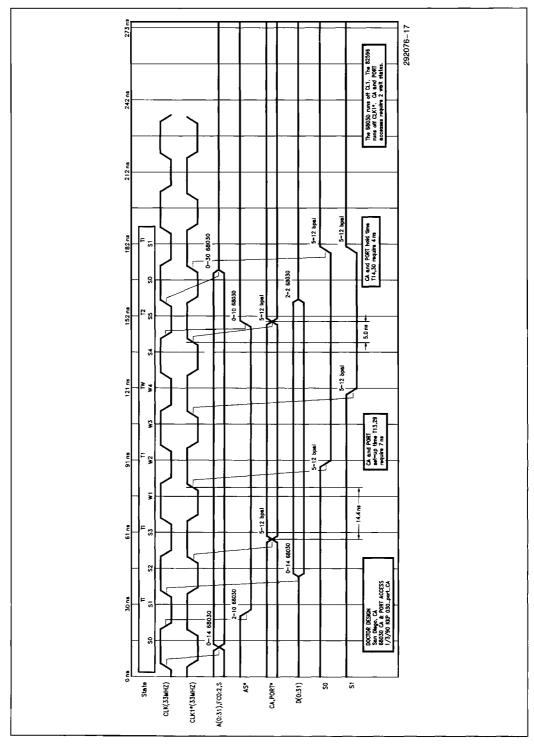

| Figure 7  | Arbiter Signal Timings                                         | . 1-503 |

| Figure 8  | Memory Signal Conversion Block Diagram                         | . 1-504 |

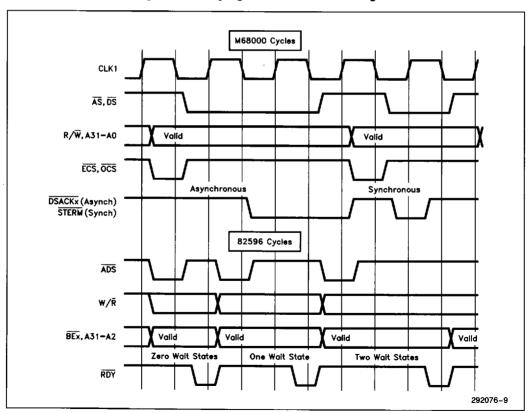

| Figure 9  | Memory Cycles for M68000 Family and 82596 Family               | . 1-504 |

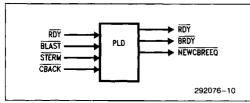

| Figure 10 | Wait-State and Burst Generation Block Diagram                  | . 1-505 |

| Figure 11 | 82596DX and 82596SX Reset Retiming Circuit                     | . 1-509 |

| TABLES    |                                                                |         |

| Table 1 8 | 32596-Family Parallel Bus Comparison                           | . 1-497 |

| Table 2   | Clocking Specifications                                        | . 1-499 |

|           | Reset Specifications                                           |         |

|           | Arbitration Signal Input Timings                               |         |

|           | Arbitration Signal Output Timings                              |         |

| Table 6 8 | 32596CA Worst-Case Reset Timing Margin                         | . 1-506 |

| Table 7 8 | 32596DX/SX Worst-Case Reset Timing Margins                     | . 1-509 |

#### 1.0 INTRODUCTION

#### 1.1 Scope

The 82596 family of LAN coprocessors provide IEEE 802.3 MAC functions for use with 10BASE5 (Ethernet), 10BASE2 (Cheapernet), 10BASE-T (Twisted Pair Ethernet), 1BASE5 (StarLAN), and other CSMA/CD LANs with serial bit rates up to 20 Mb/s. The three members of the 82596 family differ only in the characteristics of their parallel interfaces; the FIFO and serial functions are identical. Table 1 shows the parallel bus differences.

This document describes the circuits required to interface the Intel 82596 family of LAN coprocessors with the M68000 family of microprocessors. First, general interface issues are identified and then three specific designs are provided—including the PLD equations, timing diagrams, and schematics.

- 82596CA and MC68030

- 82596DX and MC68020

- 82596SX and MC68000

#### 1.2 Fundamental Assumptions

Each design is based on several fundamental assumptions about the memory subsystem. The circuits required to support these features are implemented in a few programmable components. If the 82596 is added to existing designs in which the required circuits are already implemented, these circuits do not have to be duplicated.

The following assumptions are made about the designs.

- The memory subsystem uses DRAM.

- Refresh request signals are asynchronous to the system clock.

- Interface logic is implemented in PLDs where possible.

- 82596 family type signals will be converted to M68000 family type signals.

### 2.0 GENERIC IMPLEMENTATION ISSUES

#### 2.1 Block Definitions

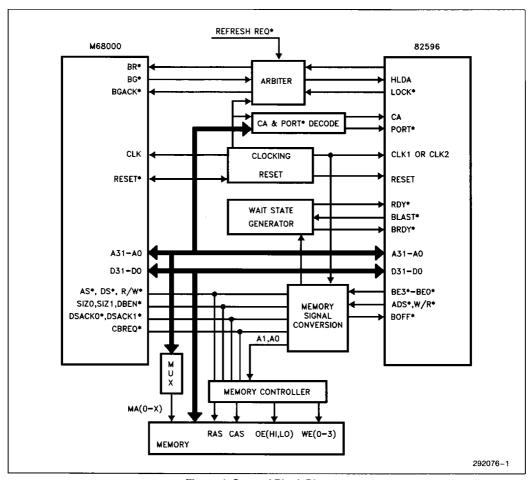

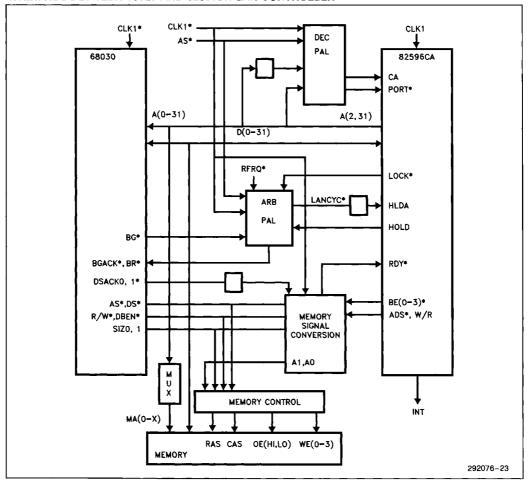

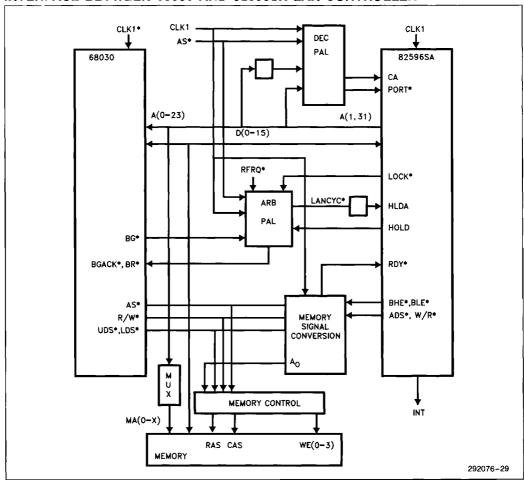

Each design is broken into functional blocks. The generic block diagram is shown in Figure 1. The M68000 family and 82596 family are fixed from a functional standpoint. The designer has almost no flexibility in their connection or timing. For the purpose of these designs, the memory control block is also assumed to be fixed. It is set up only for M68000-type signals and timings. The blocks for which there is some design flexibility are grouped under the name control logic. These blocks include the following.

- Clocking. Provides the proper clock phases to the 82596 and M68000. It also provides the clock for the other blocks.

- Reset Retiming. Takes the active low RESET signal that goes to the M68000 and adjusts its timing and level to be compatible with the active high RESET for the 82596.

- CA and PORT Generation. Decodes the address lines and generates the Channel Attention (CA) and CPU Port (PORT) signals to the 82596. The system designer selects the memory addresses to be decoded to activate these signals. The amount of decode logic will vary greatly depending on the system memory map.

- Arbitration. Determines which of the three master devices has control of the local bus: the M68000, the 82596, or the refresh controller. The refresh controller has the highest priority, followed by the 82596 and then the M68000. Additional master devices are supported through simple changes to the PLD equations in this block.

- Memory Signal Conversion. Takes the 82596 control signals, such as ADS and W/R, and converts them to M68000-type control signals, such as AS, DS, and R/W.

- Wait State and Burst Generation. Generates the RDY signal to the 82596 (and BRDY for the 82596CA). It also asserts the burst request (CBREQ) to the memory controller.

Table 1. 82596-Family Parallel Bus Comparison

| 82596<br>Version | Address<br>Bits | Data<br>Bits | Parallel<br>Clocking | Burst<br>Access | Parity<br>Pins | Maximum<br>Frequency<br>(MHz) |

|------------------|-----------------|--------------|----------------------|-----------------|----------------|-------------------------------|

| 82596CA          | 32              | 32           | x1                   | Yes             | Yes            | 33                            |

| 82596DX          | 32              | 32           | x2                   | No              | No             | 33                            |

| 82596SX          | 24              | 16           | x2                   | No              | No             | 20                            |

Figure 1. General Block Diagram

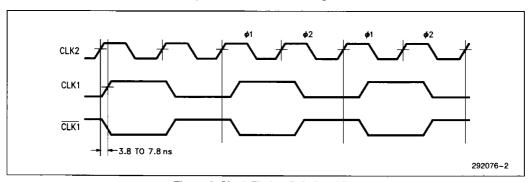

Figure 2. Clock Timing Relationships

#### 2.2 Clocking

The 82596 family uses different types of clocking. The 82596DX and 82596SX use CLK2, which is twice as fast as the internal operating frequency. The two different phases of CLK2 for every CLK1 are defined as  $\phi$ 1 and  $\phi$ 2. The rising edge of CLK1 corresponds to the rising edge of CLK2 at the beginning of  $\phi$ 1. The 82596CA uses CLK1, which is identical to the internal operating frequency. The 82596 clock timing relationships are shown in Figure 2.

In many cases the control logic is simplified by clocking it with CLK2, even if the CPU and 82596CA are clocked by CLK1. In some other cases it is advantageous to invert the clocking signal to the 82596, which introduces a phase shift between the devices. The clocking specifications of the 82596 and M68000 are shown in Table 2.

All the designs use 74F74 flip-flops because of their high operating frequency, low propagation delay, and wide availability. If another type of flip-flop is used the timing analysis must be modified to reflect the different specifications.

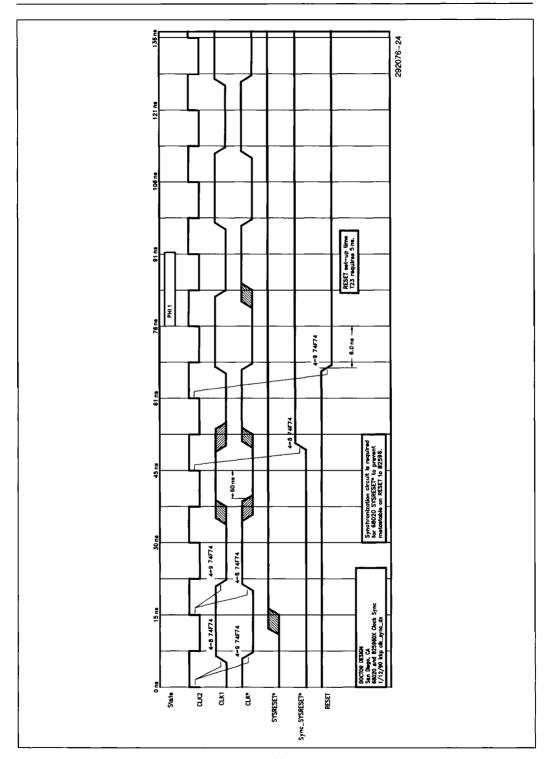

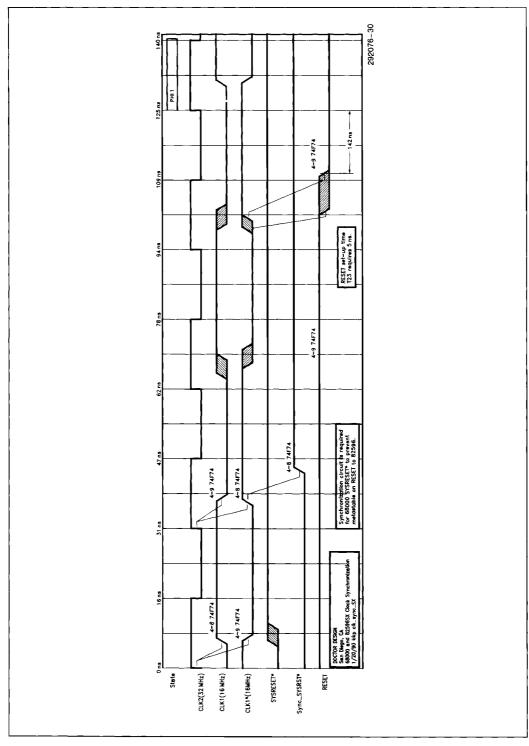

#### 2.3 Reset Retiming

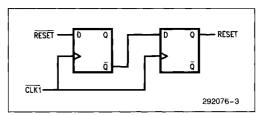

Because the 82596DX and 82596SX use CLK2, the setup and hold time specifications for the reset signal are very important. The deactivation of RESET is the only means by which the 82596DX and 82596SX determine which phases of CLK2 correspond to φ1 and φ2. Since many of the control signals are only valid at the beginning of certain phases, it is crucial that the arbitration, signal conversion, and wait state generation logic know the current phase of the clock. Failure to meet these specifications can cause improper memory accesses by the 82596. Figure 3 is the reset retiming block schematic

Figure 3. Reset Retiming Block

**Table 2. Clocking Specifications**

| Component | Freq  | Clock | Max<br>Rise | Max<br>Fall | Min<br>High | Min<br>Low |

|-----------|-------|-------|-------------|-------------|-------------|------------|

|           | (MHz) |       |             | (nanos      | econds)     |            |

| 82596CA   | 25    | CLK   | 3.0         | 3.0         | 14.0        | 14.0       |

| 82596CA   | 33    | CLK   | 3.0         | 3.0         | 11.0        | 11.0       |

| 82596DX   | 25    | CLK2  | 7.0         | 7.0         | 4.0         | 5.0        |

| 82596DX   | 33    | CLK2  | 4.0         | 3.0         | 4.5         | 4.5        |

| 82596SX   | 16    | CLK2  | 8.0         | 8.0         | 5.0         | 7.0        |

| MC68030   | 25    | CLK   | 4.0         | 4.0         | 19.0        | 19.0       |

| MC68030   | 33    | CLK   | 3.0         | 3.0         | 14.0        | 14.0       |

| MC68020   | 25    | CLK   | 4.0         | 4.0         | 19.0        | 19.0       |

| MC68020   | 33    | CLK   | 3.0         | 3.0         | 14.0        | 14.0       |

| MC68000   | 16    | CLK   | 5.0         | 5.0         | 27.0        | 27.0       |

The timings for the M68000 active low signal  $\overline{RESET}$  are not compatible with the 82596 active high signal RESET. To prevent possible metastable conditions, the M68000  $\overline{RESET}$  passes through a two-stage synchronizer before going to the 82596. This will usually require two 74F74 flip-flops. Using two stages, rather than one, greatly reduces the probability of metastable conditions in the 82596. One of the stages is also used to invert the signal. Table 3 lists the relevant specifications for  $\overline{RESET}$ .

**Table 3. Reset Specifications**

| Component | Freq<br>(MHz) | Setup<br>(ns) | Hold<br>(ns) |

|-----------|---------------|---------------|--------------|

| 82596CA   | 25            | 8.0           | 3.0          |

| 92596CA   | 33            | 10.0          | 3.0          |

| 82596DX   | 25            | 10.0          | 3.0          |

| 82596DX   | 33            | 8.0           | 3.0          |

| 82596SX   | 16            | 13.0          | 4.0          |

| MC68030   | 25            | ND            | ND           |

| MC68030   | 33            | ND            | D            |

| MC68020   | 25            | NĐ            | ND           |

| MC68020   | 33            | ND            | ND           |

| MC68000   | 16            | ND            | ND           |

ND = Not Defined by Motorola

#### 2.4 CA and PORT Generation

The 82596 has two inputs that do not correspond to any signals generated by the CPU: Channel Attention (CA) and CPU Port (PORT). Channel Attention is always monitored by the 82596, and the falling edge is internally latched. The 82596 responds to Channel Attention by reading the system control block command word, which is stored in memory. Several fields in this command word tell the 82596 what to do; e.g., acknowledge interrupts, change the state of the command unit, change the state of the receive unit, or load the bus throttle timers.

When the 82596 does not have the bus, it examines PORT. If it is active the value on the data bus is stored in the 82596 in a special register. The value on the 4 least significant bits (D3-D0) indicates one of sixteen

functions. Only four functions are defined (functions 4 through 15 are reserved and should not be used).

- 0 Do an internal reset (pins D31-D4 are ignored).

- 1 Do a self test (the results are placed at the location specified by pins D31-D4).

- 2 Execute a Dump command (the results are placed at the location specified by pins D31-D4).

- 3 Move the system configuration pointer to the location specified on pins D31-D4.

PORT has more stringent requirements for setup and hold times than CA does. PORT must meet specific setup and hold times with respect to the clock and must also be active for at least two consecutive clocks. CA is only required to be active for two clocks without meeting specific setup or hold times; however, CA only has to be active for one clock if the setup and hold times are met.

Because the M68000 family does not support a separate I/O address space, all I/O functions must be memory-mapped. The addresses for CA and PORT can be selected by the designer. In the design examples, Section 3 through 5, part of one PLD is used to generate both signals. The number of input pins on the PLD will determine the address range limitations. If the PLD has fewer input pins than the number of address lines to be decoded, one of the PLD inputs should be connected to the output of a secondary decoder. This secondary decoder must meet a worst-case propagation delay, which is listed in the comment fields of the PLD equations for each design.

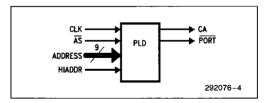

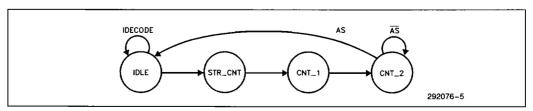

Implementing CA and PORT will usually require four macro-cells, which is about one-half of a standard PLD. Two are used for the actual output signals and two are used as a state machine to control the timing of the output signals. Figure 4 is the CA and PORT generator block diagram and Figure 5 is the state transition diagram.

Figure 4. CA and PORT Block Diagram

Figure 5. CA and PORT State Transition Diagram

#### 2.5 Arbitration

All the design examples assume that the memory will use DRAMs. This means there will be at least three master devices attempting to gain access to memory: the M68000 CPU, the 82596 LAN coprocessor, and the refresh controller. The requests from the refresh controller must be given highest priority to avoid corrupting data in the DRAMs. The 82596 is given the second highest priority, so it is not forced to wait and eventually overrun or underrun. The M68000 has the lowest priority because of its internal Bus Request/Bus Grant mechanism. Because some of the M68000 family CPUs have an internal cache or instruction pipeline, they can fetch code or data internally while the 82596 or the refresh controller are using the local bus.

The M68000 family uses a three-signal arbitration scheme. A master device makes a bus request by asserting  $\overline{BR}$  and waiting for the M68000 to assert  $\overline{BG}$ . The master device then drives  $\overline{BGACK}$  while it is using the bus. When the master device no longer needs the bus it brings  $\overline{BR}$  inactive, then the M68000 drives  $\overline{BG}$  inactive. Finally the master device drives  $\overline{BGACK}$  inactive.

#### 2.5.1 REFRESH REQUESTS

Refresh requests are assumed to be asynchronous with the arbitration clock; therefore, the refresh signal must be synchronized—typically with a 74F74 flip-flop. At the completion of the refresh cycle the local bus will be released to the requestor having highest priority. The flip-flop is not needed if the refresh request timing is synchronous with the arbitration clock and meets the setup and hold times of the PLD.

If a refresh request arrives while the M68000 is the active bus master, the Bus Request signal  $(\overline{BR})$  to the M68000 will be asserted. When the M68000 forces  $\overline{BG}$  active the arbitration logic brings  $\overline{BGACK}$  active and the refresh cycle begins. When the refresh has been completed  $\overline{BR}$  goes inactive. If the 82596 is the active bus master when the refresh request arrives, the refresh cycle will not start until the 82596 has completed its transfers.  $\overline{BR}$  to the M68000 will remain active until the refresh cycle has completed;  $\overline{BR}$  will not deassert when the 82596 completes its transfers. If another 82596 request arrives during the refresh cycle,  $\overline{BR}$  will remain active until both the refresh controller and the 82596 complete their transfers.

The designer is responsible for ensuring that enough refresh requests are made to avoid corrupting data in the DRAM. These designs assume that a refresh cycle signal goes into the memory controller and indicates that a refresh cycle is in progress. If a transparent technique is used for refreshing the DRAM, or if SRAM is used, then the arbiter can be greatly simplified.

There are several transparent DRAM refresh techniques. The most common method hides the refresh cycle as extra wait states in the normal CPU or 82596 accesses. This technique eliminates the arbitration overhead of the BR/BG (HOLD/HLDA) protocol and simplifies the arbiter logic. The main disadvantage is that the wait state generator becomes more complex.

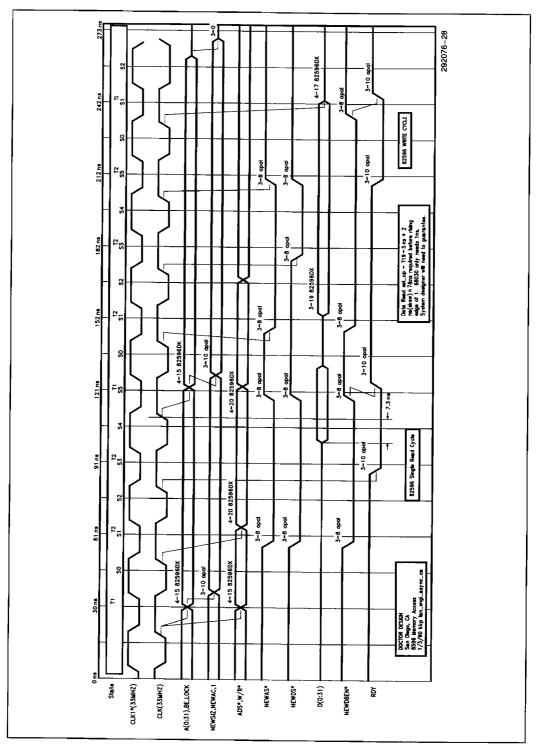

#### 2.5.2 82596 REQUESTS

The 82596 acquires and holds the system bus via the HOLD/HLDA handshake. It requests the bus by activating HOLD. When the arbiter gives the local bus to the 82596 it asserts the HLDA signal, which is the inverted LANCYC signal from the arbiter. Overrun conditions can occur in some external devices if the 82596 holds the bus too long. The 82596's bus throttle timers can be used to regulate bus use; the timer can be activated two ways.

- Externally. A high state on the BREQ pin starts the timer.

- Internally. A high state on the HLDA pin starts the timer.

Instead of using bus arbitration schemes, the 82596CA can be forced off the bus by activating the backoff pin (BOFF). This provides higher performance and faster refresh cycles. (The 82596DX and 82596SX do not have this backoff feature.)

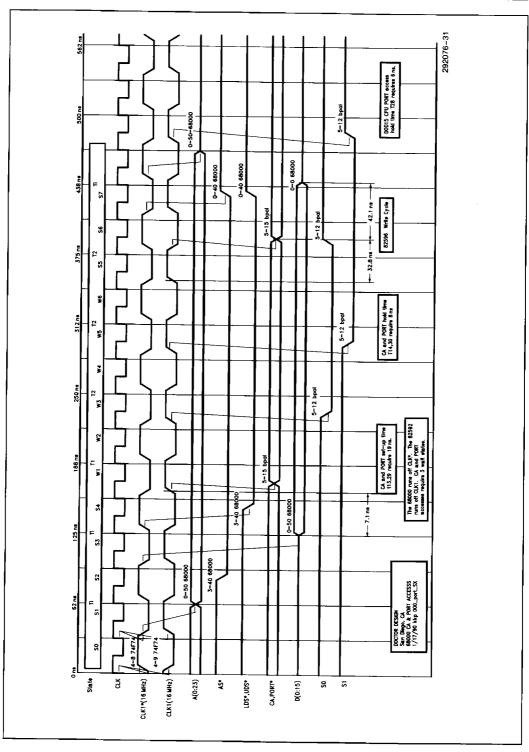

Because the 82596 HOLD and HLDA signals are active high and the M68000  $\overline{BR}$  and  $\overline{BG}$  are active low, the arbiter must invert the logic. In addition, the timings are not compatible. The arbitration signal timings are shown in Tables 4 and 5.

**Table 4. Arbitration Signal Input Timings**

| Component | Frequency<br>(MHz) | Signal | Output Valid<br>Delay (ns) |

|-----------|--------------------|--------|----------------------------|

| 82596CA   | 25                 | HOLD   | 3 to 22                    |

| 82596CA   | 33                 | HOLD   | 3 to 19                    |

| 82596DX   | 25                 | HOLD   | 4 to 22                    |

| 82596DX   | 33                 | HOLD   | 3 to 19                    |

| 82596SX   | 16                 | HOLD   | 4 to 32                    |

| MC68030   | 25                 | BG     | 0 to 20                    |

| MC68030   | 33                 | BG     | 0 to 20                    |

| MC68020   | 25                 | BG     | 0 to 20                    |

| MC68020   | 33                 | BG     | 0 to 20                    |

| MC68000   | 16                 | BG     | 0 to 40                    |

#### 2.5.3 ARBITER IMPLEMENTATION

Local bus arbitration is mostly implemented in a synchronous PLD that uses the inverted CPU clock (CLK1) as the arbitration clock. The arbiter has fixed priorities and responds to bus requests from the 82596 and the refresh controller by requesting the local bus from the M68000. The arbiter asserts the Bus Request (BR) and Bus Grant Acknowledge (BGACK) signals to the M68000, and enforces the bus arbitration protocol.

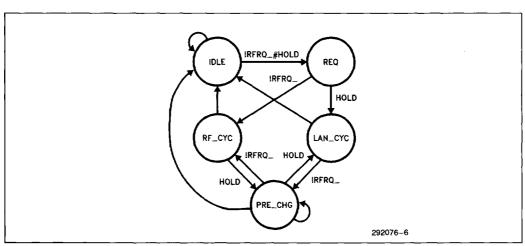

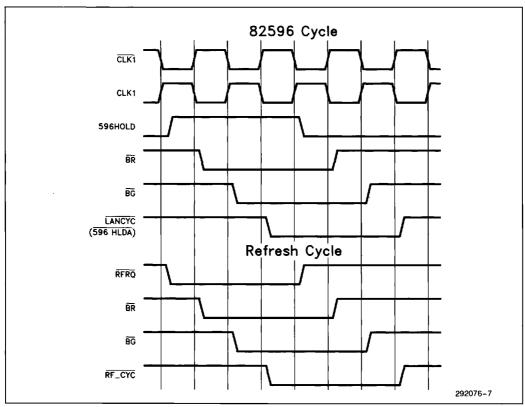

The arbiter does not immediately give the bus to the requestor. The arbiter is usually required to provide an adequate DRAM precharge time and will not release the bus until the precharge time has expired. The arbiter can be greatly simplified if other logic is used to control the precharge time. Figure 6 is the arbiter state transition diagram and the signal timings are shown in Figure 7.

**Table 5. Arbitration Signal Output Timings**

| Component | Frequency<br>(MHz) | Signal | Minimum<br>Setup (ns) | Minimum<br>Hold (ns) |

|-----------|--------------------|--------|-----------------------|----------------------|

| 82596CA   | 25                 | HLDA   | 10                    | 3                    |

| 82596CA   | 33                 | HLDA   | 8                     | 3                    |

| 82596DX   | 25                 | HLDA   | 10                    | 3                    |

| 82596DX   | 33                 | HLDA   | 8                     | 3                    |

| 82596SX   | 16                 | HLDA   | 11                    | 8                    |

| MC68030   | 25                 | BR     | NA                    | NA                   |

| MC68030   | 25                 | BGACK  | NA                    | NA                   |

| MC68030   | 33                 | BR     | NA                    | NA                   |

| MC68030   | 33                 | BGACK  | NA                    | NA                   |

| MC68020   | 25                 | BR     | NA                    | NA                   |

| MC68020   | 25                 | BGACK  | NA                    | NA                   |

| MC68020   | 33                 | BR     | NA                    | NA                   |

| MC68020   | 33                 | BGACK  | NA                    | NA                   |

| MC68000   | 16                 | BR     | NA                    | NA                   |

| MC68000   | 16                 | BGACK  | NA                    | NA                   |

Figure 6. Arbiter State Transition Diagram

Figure 7. Arbiter Signal Timings

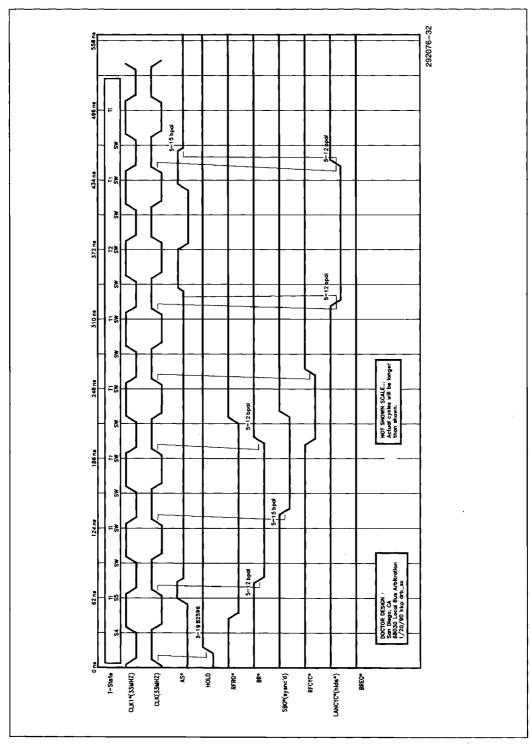

#### 2.6 Signal Conversion

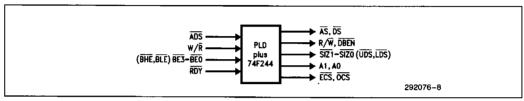

The memory signal conversion block modifies the 82596 bus signals to simulate M68000 signals. The new bus control signals are connected directly to the M68000's control signals and are tri-stated when the 82596 is not the bus master. This block will vary depending on which M68000 and 82596 combination is used. This block can be greatly simplified if the memory controller is capable of using both M68000 and 82596 signals and timings. The memory signal conversion block diagram is shown in Figure 8.

A single PLD generates the signals Address Strobe (AS), Data Strobe (DS), Read/Write (R/W), and Data Bus Enable (DBEN) from the 82596's signals ADS and W/R. In 32-bit designs this PLD also generates SIZO, SIZ1, AO, and A1 from the 82596's BEO-BE3. In 16-bit designs it generates UDS and LDS from the 82596SX's A1, BHE, and BLE signals. The External Cycle Start (ECS) and Operating Cycle Start (OCS) signals are emulated with a tri-state buffer (e.g., a 74F244) enabled by LANCYC. The input that corresponds to the ECS and OCS signals is ADS from the 82596. Figure 9 shows the different types of cycles for the M68000 and 82596.

Figure 8. Memory Signal Conversion Block Diagram

Figure 9. M68000 and 82596 Cycles

#### 2.7 Wait State and Burst Generator

#### 2.7.1 GENERAL INFORMATION

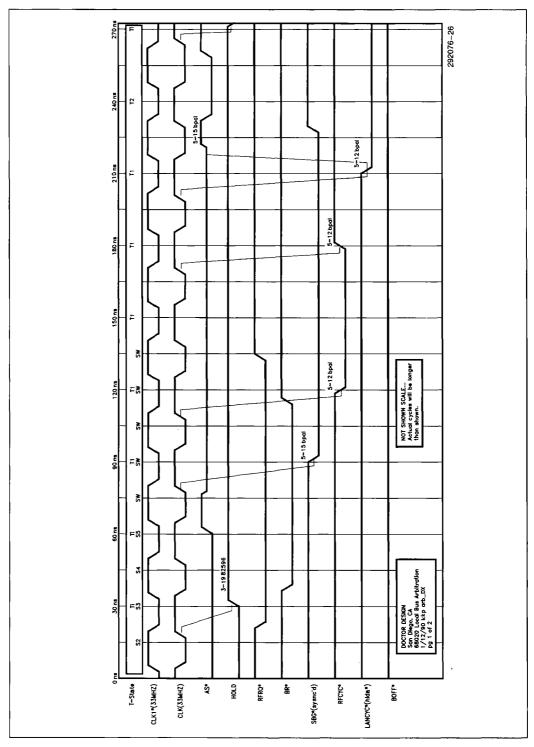

The 82596 and M68000 combinations can use three types of bus transfers (the 82596DX and 82596SX support only a basic single-cycle transfer). More than one single transfer can occur without interruption. Each transfer requires at least two clocks and begins with  $\overline{ADS}$  going active during the first clock cycle and then  $\overline{RDY}$  goes active in the last clock. Wait states are inserted by keeping  $\overline{RDY}$  inactive. Figure 10 shows the wait state and burst generator block diagram.

Figure 10. Wait-State and Burst Generator Block Diagram

The 82596CA supports all three types of transfers: single cycle, multiple cycle, and burst. The multiple cycle is simply several uninterrupted single-cycle transfers, with each bus cycle beginning with  $\overline{ADS}$  going active during the first clock and then  $\overline{RDY}$  going active in the last clock. Burst cycles can contain as many as four consecutive data transfers to four consecutive locations; however,  $\overline{ADS}$  is only generated before the first data transfer. The maximum amount of data moved during a burst is 16 bytes (four 4-byte transfers). The wait state and burst generation block inserts the appropriate number of wait states during the bus cycle by driving  $\overline{RDY}$  and  $\overline{BRDY}$  active at the appropriate time.

The M68000 family supports a 3-clock asynchronous cycle. The MC68030 also supports a 2-clock synchronous cycle that is similar to the 82596CA burst access.

#### 2.7.2 SINGLE-CYCLE BUS TRANSFERS

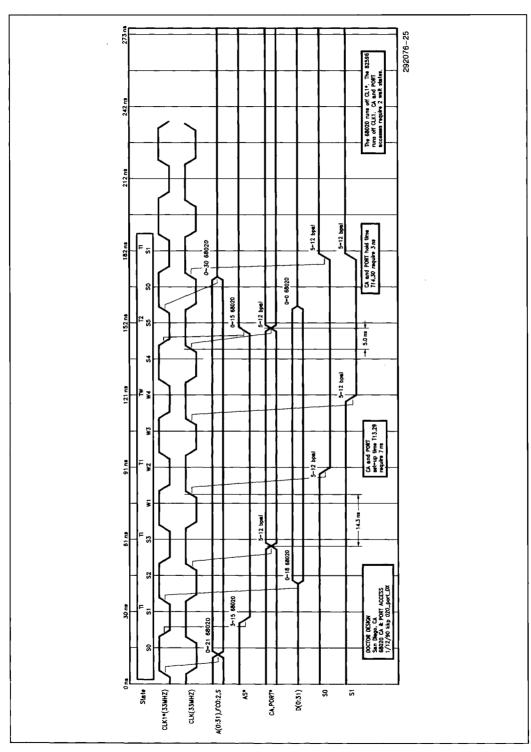

The 82596 begins a cycle after the rising edge of CLK2 (CLK for the 82596CA) by asserting ADS and driving W/R and the address lines (A31-A2) valid. The conversion PLD synchronizes ADS to the clock and generates an address strobe (NEWAS). NEWAS is asserted during the same phase of the clock that a M68000 would assert AS. NEWAS is also asserted during the second clock of the 82596 transfer.

The wait state generator delays the RDY signal to the 82596 from going active. This provides time to meet the data setup and hold specifications. The 82596 requires that data be set up a few nanoseconds before the rising edge of its clock. The M68000 also requires a setup time; however, it is usually only one nanosecond. The system designer will need to make provision for, at the least, the 82596 data setup time plus an additional 2 ns for clock skew. If this cannot be met another wait state will be needed for all 82596 memory read cycles. This can be provided by modifying the PLD equations to delay the assertion of RDY by one or more clocks at the end of a read cycle. The 82596CA asserts Burst Last (BLAST) during the second clock of the first cycle, which indicates that the transfer is complete after a single cycle (the 82596DX and 82596SX do not use BLAST).

### 2.7.3 BURST-CYCLE AND MULTIPLE-CYCLE BUS TRANSFERS

The 82596CA tries to burst cycles for any bus request that requires more than a single data cycle to consecutive addresses. The starting address must begin on an 8-byte boundary (xxxxxxx0h or xxxxxxx8h). The fastest burst cycle for this design assumes that 80 ns interleaved DRAMs are being used, which are fast enough to allow new data to be strobed into the 82596CA on each clock. The burst cycle requires 4 clocks for the first data strobe; however, subsequent data strobes are returned with each clock.

Burst cycles begin with the 82596CA driving a valid address and asserting ADS in the same manner as nonburst cycles. The 82596CA indicates that it is willing to enter a burst cycle by holding BLAST inactive during the second clock of the cycle. The ready logic then generates a Cache Burst Request (NEWCBREQ) signal to the memory controller. If Cache Burst Acknowledge (CBACK) is returned active it indicates that the memory can operate in burst mode. Then the ready logic waits for the Synchronous Termination (STERM) bus handshake signal, which indicates that the correct number of wait states has occurred and data is valid. When STERM is received the ready logic activates BRDY to the 82596CA, which indicates its willingness to allow a burst cycle. The 82596CA drives BLAST inactive for all but the last cycle in a burst. BLAST is driven active in the last cycle of the transfer to indicate that when either BRDY or RDY is next returned the transfer is complete. RDY is always returned in response to BLAST going active.

If the memory controller cannot perform a burst cycle  $\overline{CBACK}$  will not go active and the ready logic will return  $\overline{RDY}$  to the 82596CA, which indicates a nonburst multiple-cycle transfer will take place. Unlike the burst cycle,  $\overline{ADS}$  will go active at the beginning of the second and  $\overline{ADS}$  will go active at the multicycle transfer and  $\overline{RDY}$  is used to end the cycle rather than  $\overline{BRDY}$ .

The two data acknowledge signals for the MC68030 (DSACK0 and DSACK1) can be combined because the 82596CA only needs one RDY signal. Both DSACK signals connect to the inputs of an 74F08 AND gate.

#### 3.0 MC68030/82596CA INTERFACE

#### 3.1 Design Specifications

This interface example is based on the following assumptions.

- MC68030 CPU.

- 82596CA LAN coprocessor.

- 32-bit DRAM memory with burst capability.

- DRAM refresh using CAS-before-RAS technique.

- 33 and 25 MHz operating frequencies.

- Interface logic implemented in PLDs where possible.

- 82596CA signals converted to MC68030 signal types.

- Refresh request signal asynchronous to 33 MHz clock.

- · Burst accesses attempted whenever possible.

#### NOTE:

Many of the circuit elements (e.g., PLDs and flipflops) in this design probably already exist in designs presently using the MC68030. The extra elements are provided only for completeness. The final design will probably require fewer circuit elements.

#### 3.2 Clocking

This design uses a clock operating at 66 MHz. It is divided by a 74F74 flip-flop to generate two 33 MHz clocks from the Q and  $\overline{Q}$  outputs: CLK1 and  $\overline{\text{CLK1}}$ . The MC68030 uses CLK1, but the 82596CA and arbitration logic use  $\overline{\text{CLK1}}$ . The clock-to-output-valid delay of the 74F74 is 3.8 to 7.8 ns.

#### 3.3 Reset Retiming

The 82596CA reset retiming block is the same as that shown in Figure 2. The synchronizing flip-flops are clocked by CLK1. There are two 82596CA specifications for RESET that must be met: the setup time (T23) and the hold time (T24). The worst-case margin is shown in Table 6 (all times are in nanoseconds).

#### 3.4 CA and PORT Generator

The CA and PORT generation block is the same as that shown in Figure 4 and is based on a 20R4 PLD (10 ns delay at 33 MHz, 15 ns delay at 25 MHz). At either speed it is clocked by CLK1. AS, the address lines, and HIADDR are examined at the rising edge of CLK1. The worst-case margin to this rising edge limits the maximum propagation delay of the secondary decoder. Each margin is calculated separately.

Because  $\overline{AS}$  is generated later than the address, it is checked first. The setup time margin to the PLD's flipflop is calculated as follows (all times are in nanoseconds).

Table 6. 82596CA Worst-Case Reset Timing Margin

| 82596CA   | Clock-to-Output Delay |               | Minimum | Minimum | Margin |      |  |

|-----------|-----------------------|---------------|---------|---------|--------|------|--|

| Frequency | Minimum               | Minimum       | Setup   | Hold    | Setup  | Hold |  |

| (MHz)     |                       | (nanoseconds) |         |         |        |      |  |

| 33        | 3.8                   | 7.8           | 8.0     | 3.0     | 14.2   | 0.8  |  |

| 25        | 3.8                   | 7.8           | 10.0    | 3.0     | 22.2   | 0.8  |  |

The address has an additional margin because it is generated almost one-half clock earlier. This additional margin is calculated as follows.

CLK1 cycle + CLK1 high time

- max MC68030 address valid delay

- max CLK1 to CLK1 skew (3.2)

- min PLD setup

At 33 MHz =

$$30 + 15 - 21 - 2 - 10 = 12$$

ns (with 10 ns PLD)

At 25 MHz =

$$40 + 20 - 25 - 2 - 15 = 18$$

ns

(with 15 ns PLD)

Next, the worst-case setup and hold times to the 82596CA are calculated for CA and  $\overline{PORT}$ , which have identical timings. They go active based on the rising edge of  $\overline{CLK1}$ . The setup margins are calculated as follows.

(with 15 ns PLD)

The hold margins are calculated as follows.

min PLD output valid delay —

min 82596CA input hold

$$= 4 - 3 = 1$$

ns (at 33 and 25 MHz) (3.4)

#### 3.5 Bus Arbiter

The bus arbiter is implemented with a 20R8 PLD (10 ns delay at 33 MHz, 15 ns delay at 25 MHz). At either speed, it is clocked by CLK1. The worst-case flip-flop setup margins to this rising edge is calculated as follows.

The signal  $\overline{BR}$  does not need to meet any setup or hold times because it is internally synchronized by the MC68030. The PLD flip-flop setup time for  $\overline{BG}$  is checked next. Because  $\overline{BG}$  can go active 0 ns after the

(with 15 ns PLD)

falling edge of CLK1, and because there can be up to 2 ns of skew between CLK1 and  $\overline{\text{CLK1}}$ , it is not completely safe to directly use  $\overline{\text{BG}}$  in the arbiter PLD. Instead it is run through one of the flip-flops in the PLD to fully synchronize the signal. In the worst case,  $\overline{\text{BG}}$  can go active about the same time as  $\overline{\text{CLK1}}$  goes high. Because the PLD will not be clocked until the next rising edge of  $\overline{\text{CLK1}}$ , there will be at least one full clock cycle minus the PLD feedback delay for the output to reach a valid state.

The unused macro-cell in the 20R8 can be used to invert LANCYC to create HLDA to the 82596CA. The outputs of the arbiter, HLDA and REFCYC, are internally synchronized at their destination, so no output timing analysis is required.

## 1

#### 3.6 Memory Signal Conversion

The memory signal conversion block is implemented as shown in Section 2.6. A 20R4 PLD (10 ns delay at 33 MHz, 15 ns delay at 25 MHz) is used to convert the 82596CA-type control signals to MC68030-type control signals. When the 82596CA does not have the bus all the outputs go to a high-impedance state.

The signals SIZ1, SIZ0, A1, and A0 are generated by using simple combinatorial decodes of  $\overline{BE3}$ ,  $\overline{BE2}$ ,  $\overline{BE1}$ , and  $\overline{BE0}$ . The delay will be identical to the PLD propagation delay. The signals  $\overline{NEWAS}$ ,  $\overline{NEWDS}$ ,  $\overline{NEWDBEN}$ , and  $\overline{NEWR/W}$  are generated by using the PLD's registered outputs, which are clocked by  $\overline{CLK1}$ . Their states are determined by the state of the 82596CA's signals  $\overline{ADS}$ ,  $\overline{W/R}$ , and  $\overline{RDY}$ .

An 82596CA read or write cycle starts with  $\overline{ADS}$  going active based on the rising edge of  $\overline{CLK1}$ .  $\overline{NEWAS}$  and  $\overline{NEWDBEN}$  will go active on the next rising edge of  $\overline{CLK1}$ . If the cycle is a read cycle  $\overline{NEWDS}$  will also go active. If it is a write cycle  $\overline{NEWDS}$  will go active one clock later. In general, the signals go inactive based on  $\overline{RDY}$  going active. To meet the data hold times  $\overline{NEWDBEN}$  stays active one extra clock during a write cycle.  $\overline{NEWR/W}$  is simply the inverted and registered  $\overline{W/R}$ .

The timing of the PLD is checked next. The 82596CA control signals must be valid in time to meet the setup requirements of the PLD's flip-flops. The margin is calculated as follows.

NEWAS goes active based on the rising edge of  $\overline{\text{CLK}1}$ , which is the same as the falling edge of  $\overline{\text{CLK}1}$ . The PLD clock to output valid delay is 3 to 7 ns maximum at 33 MHz and 4 to 12 ns maximum at 25 MHz. The skew between the clocks will be -2 to +2 ns. This translates to a 1 to 5 ns delay at 33 MHz and 2 to 10 ns delay at 25 MHz, which is within the MC68030 specifications of 2 to 10 ns.

ECS and OCS are generated by taking ADS and running it through a tri-state buffer (74F244) that is enabled by HLDA. When the 82596CA has the bus ECS and OCS will go active about 4 to 8 ns after ADS goes active.

#### 3.7 Wait State and Burst Generator

#### 3.7.1 GENERAL INFORMATION

The 82596CA supports three types of bus transfers: single cycle, multiple cycle, and burst. Each bus cycle is at least two clocks long and begins with ADS going active during the first clock and RDY active in the last clock. A bus cycle contains one or more data transfers, each of which can be up to 32 bits. Burst cycles can contain as many as four data transfers, thus, the maximum amount of data moved during a burst is 16 bytes (4 transfers of 4 bytes each). The wait state and burst generation block inserts the proper number of wait states during the bus cycle. For this design it was assumed that the DRAM would allow for zero wait state accesses for the second through fourth data transfers during a burst cycle. If slower DRAMs are used, wait states will need to be inserted in the DSACK and RDY generation circuits.

#### 3.7.2 SINGLE CYCLE TRANSFERS

The fastest single cycle transfer in this design requires three clocks for the 82596CA. The 82596CA initiates a cycle after the rising edge of  $\overline{CLK1}$  by asserting  $\overline{ADS}$  and driving  $W/\overline{R}$  and the address lines (A31-A2) valid. The conversion PLD synchronizes  $\overline{ADS}$  and generates an address strobe  $(\overline{NEWAS})$ .  $\overline{NEWAS}$  is asserted during the same phase of the clock that a MC68030 would assert  $\overline{AS}$ .  $\overline{NEWAS}$  is also asserted during the second clock of the 82596CA transfer.

The wait state generator delays the  $\overline{RDY}$  signal to the 82596CA. This provides enough time to meet the data setup and hold specifications. The 82596CA requires that data be valid at least 5 ns before the rising edge of its clock. The MC68030 requires only a 1 ns setup to its clock. The system designer will need to guarantee that

the 82596CA has at least a 5 ns data setup to this edge, plus 2 ns for the clock skew. If this cannot be met, another wait state will be needed for all 82596 memory read cycles. This can be done by modifying the PLD equations to delay the assertion of RDY by one or more clocks. The 82596CA asserts Burst Last (BLAST) during the second clock of the first cycle, which indicates that the transfer is complete after a single cycle.

#### 3.7.3 BURST CYCLE BUS TRANSFERS

The 82596CA attempts burst cycles for any bus request that requires more than a single data cycle to consecutive addresses. The starting address must begin on an 8-byte boundary (xxxxxxx0h) or xxxxxxx8h). The fastest burst cycle for this design assumes 80 ns interleaved DRAMs, which allow new data to be strobed into the 82596CA on each clock. The burst cycle requires four clocks for the first data strobe, but subsequent data strobes are returned with each clock.

Burst cycles begin with the 82596CA driving a valid address and asserting ADS in the same manner as nonburst cycles. The 82596CA indicates that it is willing to enter a burst cycle by holding BLAST inactive in the second clock of the cycle. The ready logic then generates a cache burst request (NEWCBREQ) signal to the memory controller. If the cache burst acknowledge signal (CBACK) is returned active it indicates that the memory can operate in burst mode. The ready logic then waits for the synchronous termination (STERM) bus handshake signal, which indicates that the correct number of wait states has occurred and data is valid. The ready logic then activates BRDY to the 82596CA to indicate its willingness to permit a burst cycle. The 82596CA drives BLAST inactive for all but the last cycle in a burst. BLAST is driven active in the last cycle of the transfer to indicate that when RDY or BRDY is next returned the transfer is complete. RDY is always returned in response to BLAST going active.

If the memory controller cannot perform a burst cycle  $\overline{CBACK}$  will not go active and the ready logic will return  $\overline{RDY}$  to the 82596CA to indicate a nonburst multiple-cycle transfer will take place. This bus transfer is simply a sequence of two or more single cycle transfers. Unlike the burst cycles,  $\overline{ADS}$  goes active during the first clock of the second through fourth data transfers. The timing margins for these cycles are identical to those for nonburst single cycle transfers.

Because the 82596CA requires only one  $\overline{RDY}$  signal, the two data acknowledge signals for the MC68030 ( $\overline{DSACK0}$  and  $\overline{DSACK1}$ ) can be combined. Both  $\overline{DSACK}$  signals connect to the inputs of an 74F08 AND gate.

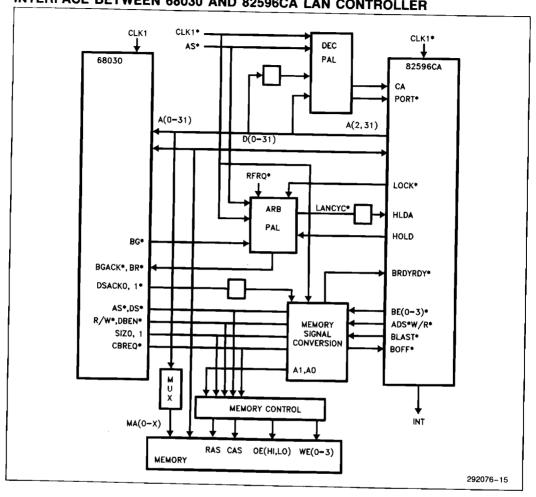

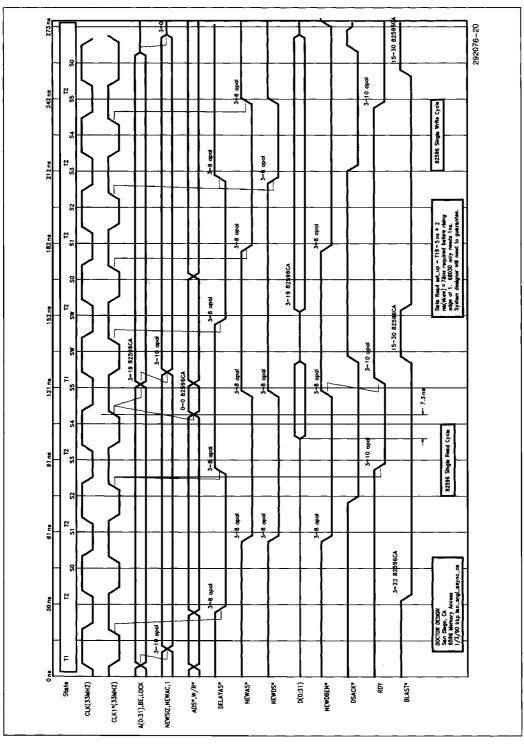

#### 4.0 MC68020/82596DX INTERFACE

#### 4.1 Design Specifications

This interface example is based on the following assumptions.

- MC68020 CPU.

- 82596DX LAN coprocessor.

- 32-bit DRAM memory without burst capability.

- DRAM refresh using CAS-before-RAS technique.

- 33 MHz operating frequency.

- Interface logic implemented in PLDs where possible.

- 82596DX signals converted to MC68020 signal types.

- Refresh request signal asynchronous to 33 MHz clock.

#### NOTE:

Many of the circuit elements (e.g., PLDs and flipflops) in this design probably already exist in designs presently using the MC68020. The extra elements are provided only for completeness. The final design will probably require fewer circuit elements.

#### 4.2 Clocking

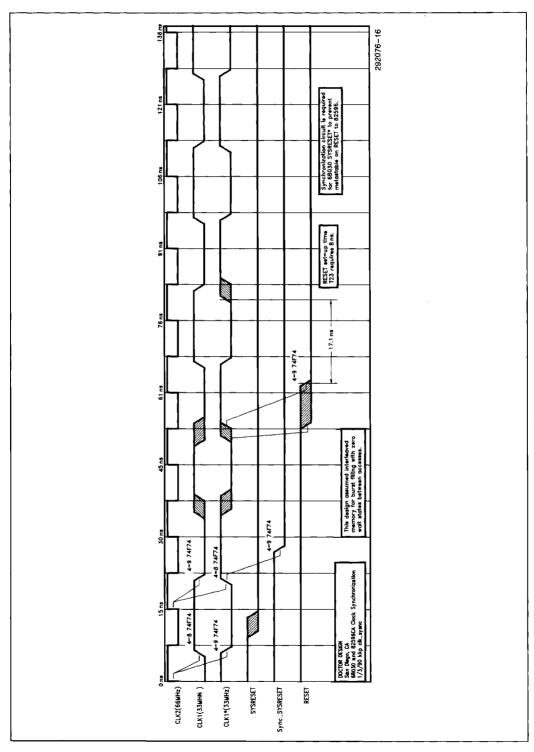

This design uses a clock operating at 66 MHz. The 66 MHz clock, CLK2, is directly by the 82596DX. It is divided by a 74F74 flip-flop to generate two 33 MHz clocks from the Q and  $\overline{Q}$  outputs: CLK1 and  $\overline{CLK1}$ . The MC68020 uses  $\overline{CLK1}$ , but the arbitration logic uses CLK1. The clock-to-output-valid delay of the 74F74 is 3.8 to 7.8 ns. The rising edge of CLK1 corresponds to the rising edge of CLK2 at the beginning of  $\phi$ 1.

#### 4.3 Reset Retiming

The 82596DX reset retiming block is shown in Figure 11. The synchronizing flip-flops are clocked by CLK2. There are two 82596DX specifications for RESET that must be met: the setup time (T23) and the hold time (T24). The worst-case margin is shown in Table 7.

Figure 11. Reset Retiming Block

Table 7. 82596DX/SX Worst-Case Reset Timing Margin

| 82596<br>Frequency | Clock-to-O | utput Delay | Minimum    | Minimum | Mar   | gin  |

|--------------------|------------|-------------|------------|---------|-------|------|

|                    | Minimum    | Maximum     | Setup      | Hold    | Setup | Hold |

| (MHz)              |            |             | (nanosecon | ds)     |       |      |

| 33                 | 3.8        | 7.8         | 8.0        | 3.0     | 14.2  | 0.8  |

| 25                 | 3.8        | 7.8         | 10.0       | 3.0     | 22.2  | 8.0  |

| 16                 | 3.8        | 7.8         | 13.0       | 4.0     | 45.2  | -0.2 |

#### 4.4 CA and PORT Generator

The CA and PORT generation block is the same as that shown in Figure 4 and is based on a 20R4 PLD (10 ns delay at 33 MHz, 15 ns delay at 25 MHz) clocked by CLK1. AS, the address lines, and HIADDR are examined at the rising edge of CLK1. The worst-case margin to this rising edge limits the maximum propagation delay of the secondary decoder. Each margin is calculated separately.

Because  $\overline{AS}$  is generated later than the address, it is checked first. The setup time margin to the PLD's flipflop is calculated as follows (all times are in nanoseconds).

At 33 MHz =

$$30 - 15 - 2 - 10 = 3$$

ns

(with 10 ns PLD)

At 25 MHz =

$$40 - 18 - 2 - 15 = 5$$

ns

(with 15 ns PLD)

The address has an additional margin because it is generated almost one-half clock earlier. This additional margin is calculated as follows.

At 33 MHz =

$$30 + 15 - 21 - 2 - 10 = 12$$

ns (with 10 ns PLD)

At 25 MHz =

$$40 + 20 - 25 - 2 - 15 = 18 \text{ ns}$$

(with 15 ns PLD)

Next, the worst-case setup and hold times to the 82596DX are calculated for CA and PORT, which have identical timings. They go active based on the rising edge of CLK1. The setup margins are calculated as follows.

At 33 MHz =

$$30 - 7 - 7 - 7.8 = 8.2$$

ns (with 10 ns PLD)

At 25 MHz =

$$40 - 12 - 7 - 7.8 = 13.2$$

ns (with 15 ns PLD)

The hold margins are calculated as follows.

PLD output valid delay - min 82596DX input hold

+ min CLK2 to CLK1 skew (4.4)

=

$$4 - 3 + 3.8 = 4.8$$

ns (at 33 and 25 MHz)

#### 4.5 Bus Arbiter

The bus arbiter is implemented with a 20R8 PLD (10 ns delay at 33 MHz, 15 ns delay at 25 MHz) clocked by CLK1. The worst-case margins to this rising edge is calculated as follows.

At 33 MHz =

$$30 + 3.8 - 19 - 10 = 4.8 \text{ ns}$$

(with 10 ns PLD)

At 25 MHz =

$$40 + 3.8 - 22 - 15 = 7.8$$

ns (with 15 ns PLD)

The signal  $\overline{BR}$  does not need to meet any setup or hold times because it is internally synchronized by the MC68020. The PLD flip-flop setup time for  $\overline{BG}$  is checked next. Because  $\overline{BG}$  can go active 0 ns after the falling edge of  $\overline{CLK1}$ , and because there can be up to 2 ns of skew between CLK1 and  $\overline{CLK1}$ , it is not completely safe to directly use  $\overline{BG}$  in the arbiter PLD. Instead it is run through one of the flip-flops in the PLD to fully synchronize the signal. In the worst case,  $\overline{BG}$  can go active about the same time as CLK1 goes high. Because the arbiter's flip-flop will not be clocked until the next rising edge of CLK1, there will be a full clock cycle minus the PLD feedback delay for the output to reach a valid state.

The outputs of the arbiter, LANCYC and REFCYC, are internally synchronized at their destination, so no output timing analysis is required. An external inverter is required for LANCYC to create HLDA to the 82596DX. If the PLD has an internal inverter then this will not be required.

#### 4.6 Memory Signal Conversion

The memory signal conversion block is implemented as shown in Section 2.6. A 20R4 PLD (10 ns delay at 33 MHz, 15 ns delay at 25 MHz) is used to convert the 82596DX-type control signals to MC68020-type control signals. When the 82596DX does not have the bus all the outputs go to a high-impedance state.

The signals SIZ1, SIZ0, A1, and A0 are generated by using simple combinatorial decodes of \$\overline{BE3}\$, \$\overline{BE2}\$, \$\overline{BE2}\$, \$\overline{BE2}\$, \$\overline{BE2}\$, \$\overline{BE2}\$, and \$\overline{BE0}\$. The delay will be identical to the PLD propagation delay. The signals \$\overline{NEWDS}\$, \$\overline{NEWDS}\$, \$\overline{NEWDS}\$, and \$\overline{NEWR/W}\$ are generated by using the PLD's registered outputs, which are clocked by CLK1. Their states are determined by the state of the \$2596DX's signals \$\overline{ADS}\$, \$\overline{W/R}\$, and \$\overline{RDY}\$.

An 82596DX read or write cycle starts with  $\overline{ADS}$  going active based on the rising edge of CLK1. NEWAS and NEWDBEN will go active on the next rising edge of CLK1. If the cycle is a read cycle NEWDS will also go active. If it is a write cycle NEWDS will go active one clock later. In general, the signals go inactive based on  $\overline{RDY}$  going active. To meet the data hold times NEWDBEN stays active one extra clock during a write cycle. NEWR/ $\overline{W}$  is simply the inverted and registered  $W/\overline{R}$ .

The timing of the PLD is checked next. The 82596DX control signals must be valid in time to meet the setup requirements of the PLD's flip-flops. The margin is calculated as follows.

At 33 MHz =

$$30 + 3.8 - 19 - 10 = 4.8 \text{ ns}$$

(with 10 ns PLD)

At 25 MHz =

$$40 + 3.8 - 22 - 15 = 7.8$$

ns (with 15 ns PLD)

NEWAS goes active based on the rising edge of CLK1, which is the same as the falling edge of CLK1. The PLD clock to output valid delay is 2 to 7 ns maximum. The skew between the clocks will be -2 to +2 ns. This translates to a 0- to 5 ns delay, which is within the MC68020 specifications of 2 to 10 ns.

$\overline{ECS}$  and  $\overline{OCS}$  are generated by taking  $\overline{ADS}$  and running it through a tri-state buffer (74F244) that is enabled by HLDA. When the 82596DX has the bus  $\overline{ECS}$  and  $\overline{OCS}$  will go active about 8 ns after  $\overline{ADS}$ .

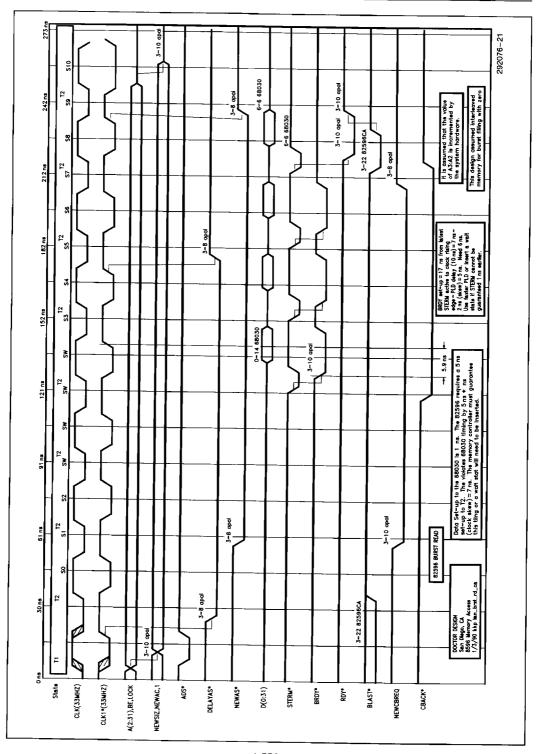

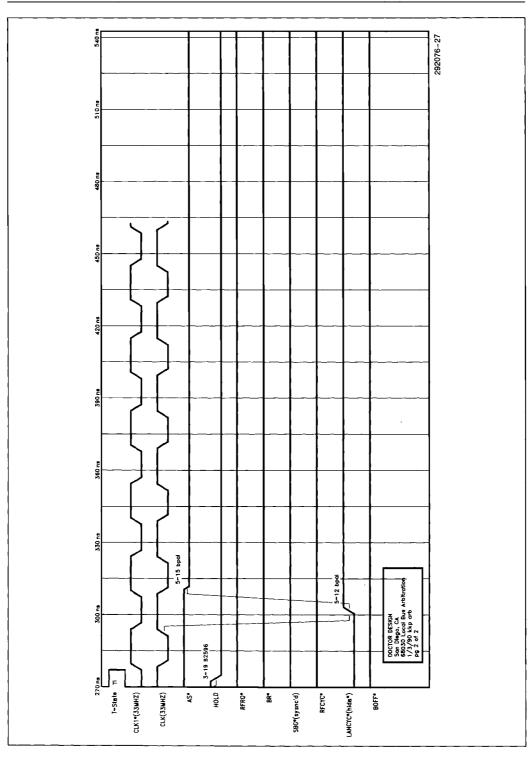

#### 4.7 Wait State Generator

Each 82596DX bus cycle is at least two clocks long and begins with  $\overline{ADS}$  going active during the first clock and

RDY active in the last clock. The wait state block inserts the proper number of wait states during the bus cycle by delaying the RDY signal to the 82596DX. The fastest single transfer in this design requires three clocks for the 82596DX. This provides enough time to meet the data setup and hold specifications. The 82596DX requires that data be valid at least 5 ns before the rising edge of its clock. The MC68020 requires only a 1 ns setup to its clock. The system designer will need to guarantee that the 82596DX has at least a 5 ns data setup to this edge, plus 2 ns for the clock skew. If this cannot be met, another wait state will be needed for all 82596DX memory read cycles. This can be done by modifying the PLD equations to delay the assertion of RDY by one or more clocks.

Because the 82596DX requires only one RDY signal, the two data acknowledge signals for the MC68020 (DSACKO) and DSACKI) can be combined. Both DSACK signals connect to the inputs of an 74F08 AND gate.

#### 5.0 MC68000/82596SX INTERFACE

#### 5.1 Design Specifications

This interface example is based on the following assumptions.

- MC68000 CPU.

- 82596SX LAN coprocessor.

- 16-bit DRAM memory without burst capability.

- DRAM refresh using CAS-before-RAS technique.

- 16 MHz operating frequency.

- Interface logic implemented in PLDs where possible.

- 82596SX signals converted to MC68000 signal types.

- Refresh request signal asynchronous to 16 MHz clock.

#### NOTE:

Many of the circuit elements (e.g., PLDs and flipflops) in this design probably already exist in designs presently using the MC68000. The extra elements are provided only for completeness. The final design will probably require fewer circuit elements.

#### 5.2 Clocking

This design uses a clock operating at 32 MHz. The 32 MHz clock, CLK2, is used directly by the 82596SX. It is divided by a 74F74 flip-flop to generate two 16 MHz clocks from the Q and  $\overline{Q}$  outputs: CLK1 and  $\overline{CLK1}$ . The MC68000 uses  $\overline{CLK1}$ , but the arbitration logic uses CLK1. The clock-to-output-valid delay of the 74F74 is 3.8 to 7.8 ns. The rising edge of CLK1 corresponds to the rising edge of CLK2 at the beginning of  $\phi$ 1.

#### 5.3 Reset Retiming

The 82596SX reset retiming block is shown in Figure 11. The synchronizing flip-flops are clocked by CLK2. There are two 82596SX specifications for RESET that must be met: the setup time (T23) and the hold time (T24). The worst-case margin is shown in Table 7 (all times are in nanoseconds).

#### 5.4 CA and PORT Generator

The CA and PORT generation block is the same as that shown in Figure 4 and is based on a 20R4-15 PLD clocked by CLK1.  $\overline{AS}$ , the address lines, HIADDR,  $\overline{LDS}$ , and CLK1 are decoded in a combinatorial macro-cell of the 20R4. The macro-cell output is sent to the input of one of the registered macro-cells, which is clocked at the rising edge of CLK1. Since propagation delay through the PLD is much less than the CLK1 cycle time, there will be a large margin on the flip-flop setup time.

Next, the worst-case setup and hold times to the 82596SX are calculated. The 82596SX timings are identical for both CA and PORT. They go active based on the rising edge of CLK1. The setup margins are calculated as follows.

Margins are calculated as follows.

#### 5.5 Bus Arbiter

The bus arbiter is implemented with a 20R8-15 PLD clocked by CLK1. The worst-case margins to this rising edge is calculated as follows.

CLK1 cycle - max 82596SX output

- min PLD input setup

+ min CLK2 to CLK1 skew

=

$$66 - 32 - 15 + 3.8 = 22.8$$

ns

The signal  $\overline{BR}$  does not need to meet any setup or hold times because it is internally synchronized by the MC68000. The PLD flip-flop setup time for  $\overline{BG}$  is checked next. Because  $\overline{BG}$  can go active 0 ns after the falling edge of  $\overline{CLK1}$ , and because there can be up to 2 ns of skew between CLK1 and  $\overline{CLK1}$ , it is not completely safe to directly use  $\overline{BG}$  in the arbiter PLD. Instead it is run through one of the flip-flops in the PLD to fully synchronize the signal. In the worst case,  $\overline{BG}$  can go active about the same time as CLK1 goes high. Because the arbiter's flip-flop will not be clocked until the next rising edge of CLK1, there will be almost 60 ns for the output to reach a valid state.

The outputs of the arbiter, <u>LANCYC</u> and <u>REFCYC</u>, are internally synchronized at their destination, so no output timing analysis is required. An inverter is required for <u>LANCYC</u> to create HLDA to the 82596SX. If the PLD has an internal inverter then this will not be required. If not, one of the unused macrocells in the 20R8 can be used to perform the inversion.

#### 5.6 Memory Signal Conversion

The memory signal conversion block is implemented as shown in Section 2.6. A 20R4-15 PLD is used to convert the 82596SX-type control signals to MC68000-type control signals. When the 82596SX does not have the bus all the outputs go to a high-impedance state.

The signals UDS, LDS, and A1 are generated by using simple combinatorial decodes of BHE and BLE. The delay will be identical to the PLD propagation delay, which is 15 ns maximum. The signals NEWAS, NEWDS, NEWDBEN, and NEWR/W are generated by using the PLD's registered outputs, which are clocked by CLK1. Their states are determined by the state of the 82596SX's signals ADS, RDY, and W/R.

An 82596SX read or write cycle starts with ADS going active based on the rising edge of CLK2. NEWAS and NEWDBEN will go active on the next rising edge of

CLK1. If the cycle is a read cycle  $\overline{\text{NEWDS}}$  will also go active. If it is a write cycle  $\overline{\text{NEWDS}}$  will go active one clock later. In general, the signals go inactive based on  $\overline{\text{RDY}}$  going active. To meet the data hold times  $\overline{\text{NEWDBEN}}$  stays active one extra clock during a write cycle.  $\overline{\text{NEWDR}}/\overline{\text{W}}$  is simply the inverted and registered  $\overline{\text{W/R}}$ .

The timing of the PLD is checked next. The 82596SX control signals must be valid in time to meet the setup requirements of the PLD's flip-flops. The margin is calculated as follows.

NEWAS goes active based on the falling edge of CLK1, which is the same as the rising edge of CLK1. The PLD clock to output valid delay is 5 to 12 ns maximum. The skew between the clocks will be -2 to +2 ns. This translates to a 3 to 14 ns delay, which is within the MC68000 specifications of 3 to 40 ns.

ECS and OCS are generated by taking ADS and running it through a tri-state buffer (74F244) that is enabled by HLDA. When the 82596SX has the bus ECS and OCS will go active about 8 ns after ADS.

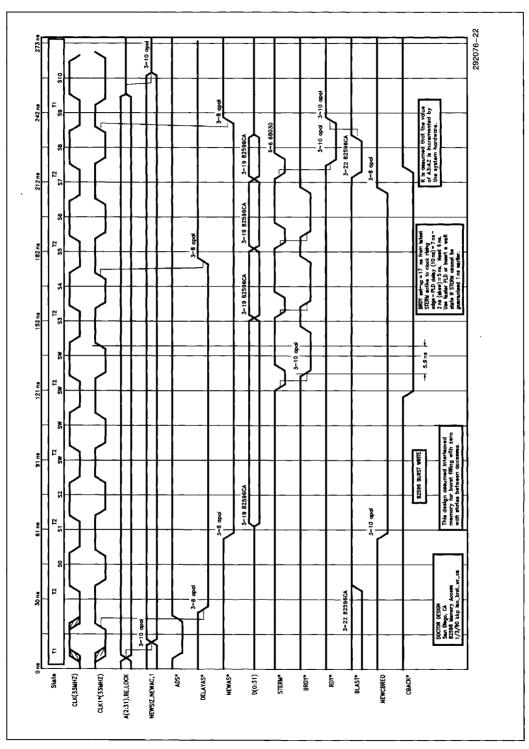

#### 5.7 Wait State Generator

The 82596SX bus cycle is at least two clocks long and begins with ADS going active during the first clock and RDY active in the last clock. The wait state generation block inserts the proper number of wait states during the bus cycle. For this design it was assumed that the DRAM would allow for zero wait state accesses. If slower DRAMs are used, wait states will need to be inserted in the DSACK and RDY generation circuits.

The fastest single cycle transfer in this design requires three clocks for the 82596SX. The wait state generator delays the  $\overline{RDY}$  signal to the 82596SX. This provides enough time to meet the data setup and hold specifications. The 82596SX requires that data be valid at least 5 ns before the rising edge of its clock. The MC68000 requires only a 1 ns setup to its clock. The system designer will need to guarantee that the 82596SX has at least a 5 ns data setup to this edge, plus 2 ns for the clock skew. If this cannot be met, another wait state will be needed for all 82596 memory read cycles. This can be done by modifying the PLD equations to delay the assertion of  $\overline{RDY}$  by one or more clocks.

1

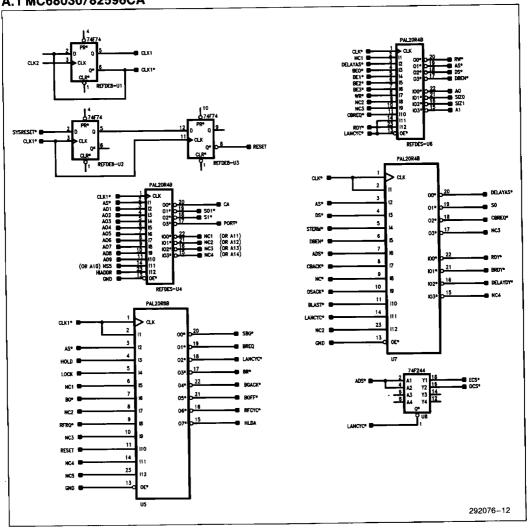

# APPENDIX A SCHEMATICS

Each schematic includes only the logic needed to interface the 82596 to the M68000. The address and data bus connections between the two are not currently shown.

#### A.1 MC68030/82596CA

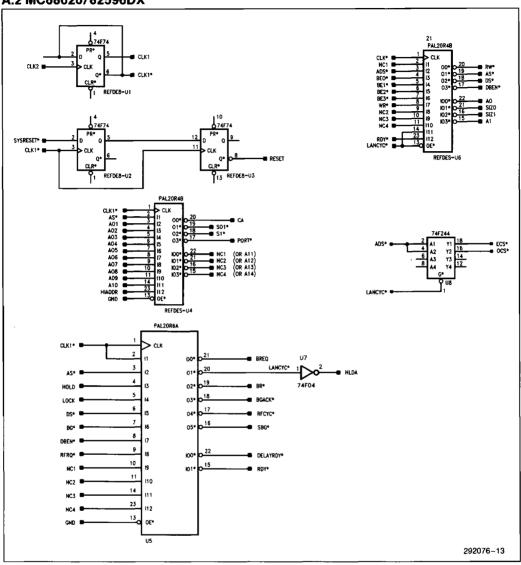

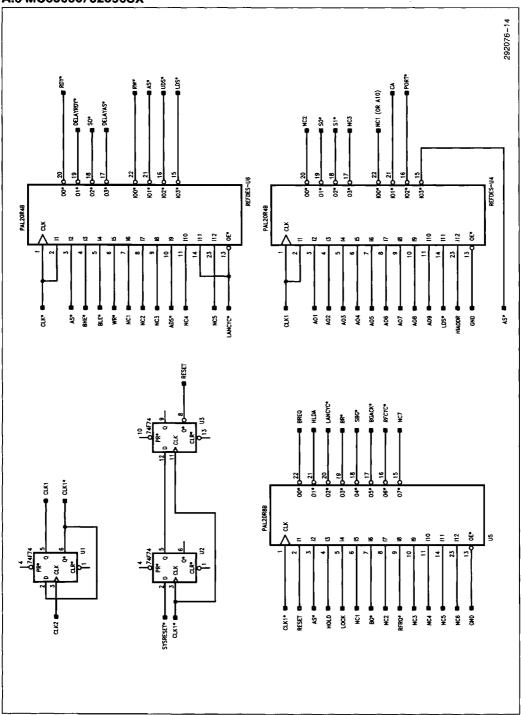

#### A.2 MC68020/82596DX

#### A.3 MC68000/82596SX

## APPENDIX B PLD EQUATIONS

Several conventions are used in the PLD equations. These are designed to make the equations easier to understand. In general the equations are designed for PLD's with fixed macro-cells. If programmable macro-cells are available, then some reduction will be possible.

Pin signal name assignments are followed by a comment indicating the pin type:

- Input = I

- Combinatorial input/output = I/O

- Registered input/output = R, I/O

Names for active low signals are followed by an underscore. For example, AS\_ is an active low signal and BREQ is an active high signal. Logical operators are defined as:

- Logical AND = &

- Logical OR = #

- Logical NOT = !

Where possible, state and truth table formats are used.

General comments start with a " in the left-most column. Specific Comments appear on the same line as the individual equations or terms within the equation. If there is not room on the right side for the comment to fit on the same line, then it will be indented on the following line.

```

B.1 MC68030/82596CA

Module ARB FLAG '-R3';

Title '82596CA Arbitration for Local Bus Rev. B 02/20/90

DOCTOR DESIGN, San Diego, CA

PLD20R8-10';

********

Descrption

********

FOR: 82596CA / 68030 Interface

This PLD arbitrates between the CPU, the LAN Controller and

the Refresh requestor for the local bus. Refresh requests are

given highest priority, and the 82596 requests given second

highest priority. The CPU normally controls the local bus

when no requests are pending.

Requestors are granted the bus by using the inverted CPU clock

(CLK1 ). Since CLK1 is also used in the equations, it must

connected with a separate pin with a separate name (CCLK1).

The refresh request (RFRQ ) is assumed to be an active low

signal having the required 12 ns set-up to the inverted clock

(CLK1 ). If this set-up cannot be guaranteed, the request

must be synchronized through an external flip-flop, clocked

with CLK1 .

SBG is the synchronized 68030 Bus Grant (BG) signal,

HLDA is the inverted LANCYC*. Due to a lack of P-terms, HLDA

will be delayed by 1 clock. If a PLD with inverter outputs is

available, then LANCYC* can be inverted and used directly as

The Bus Request signal, BREQ, and Backoff, BOFF, are used to

activiate the Bus Throttle Timers and backoff function. The

equations are included but the outputs are always set

inactive. It is left to the system designer to define input

conditions for this signal.

The two states LAN_OFF and LAN_RF can be used if the external

circuitry cannot guarantee that the 82596 will get off the bus

in time to do refresh cycles. If these states are used, a

larger PLD will be needed to generate the BGACK to the 68030.

UNUSED INPUT PINS

" UNUSED OUTPUT PINS (REGISTERED)

UNUSED OUTPUT PINS (COMBINATORIAL) : 0

```

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

```

arb Device 'P20R8';

Pin 1; "I"

VCC

Pin 24;

CLK1

Pin 2; "I"

CCLK1_

NC5

Pin 23; "I"

3; "I"

Pin 22; "R, I/O"

SBG

Pin

AS

Pin 21; "R, I/O"

4; "I"

BREQ

HOLD

Pin

LOCK

Pin

5; "I"

LANCYC

Pin 20; "R, I/O"

6; "I"

Pin 19; "R, I/O"

NC1

Pin

BR

7; "I"

Pin 18; "R, I/O"

BGACK

BG

Pin

8; "I"

NC2

BOFF

Pin 17; "R, I/O"

Pin

Pin 16; "R, I/O"

9; "I"

RFRQ_

Pin

RFCYC_

Pin 10; "I"

NC3

HLDA

Pin 15; "R, I/O"

RESET

Pin 11; "I"

NC4

Pin 14; "I"

Pin 12;

OE_

Pin 13; "I"

GND

MODE

= [BR_, BGACK_, RFCYC_, LANCYC_, BOFF_];

= [1,1,1,1,1];

IDLE

REQ

= [0,1,1,1,1];

" Generic request to CPU for local bus.

RF_CYC = [1,0,0,1,1];

" Refresh request has been granted.

" LAN request has been granted.

LAN_{CYC} = [1, 0, 1, 0, 1];

PRE_CHG = [1,0,1,1,1];

" Required for back-to-back cycles.

" The following two lines are used only if the 82596 is required to

" be kicked off the bus. Most designs will not require these states.

" LAN_OFF = [1,0,1,0,0]; Refresh Request forces 82596 off bus.

" LAN_ON = [1,0,0,1,0]; Refresh Request returns control to 82596

Equations

BREQ := 0;

" Bus Throttle conditions will need to be

" defined by the system designer.

SBG_ = !BG_ & CCLK1_

" Set synchronized bus grant during high clock

" to phase meet setup to ARB PLD.

" Hold until processor bus grant goes away.

# !SBG & !BG

# !SBG & !CCLK1 " Hold through low clock phase to met setup.

HLDA := !LANCYC_;

" Create HLDA from inverted LANCYC .

292076-36

```

```

Ì

```

```

MODE := RESET & IDLE: " Initialize state machine to IDLE State on reset.

State Diagram IN arb MODE

state IDLE : IF (!RFRQ_ # HOLD) THEN REQ

ELSE IDLE;

: CASE (!RFRQ_ & !SBG_)

state REQ

:RF_CYC;

(HOLD & RFRQ & !SBG_)

:LAN_CYC;

(!((!RFRQ_ & !SBG_)

# (HOLD & RFRQ & SBG_)))

:REQ;

ENDCASE;

state RF_CYC : CASE (RFRQ_ & !HOLD & SBG_)

:IDLE;

(RFRQ & HOLD)

:PRE CHG;

(!RFRQ_)

:RF CYC;

ENDCASE;

state LAN CYC : CASE (!HOLD & RFRQ & !LOCK & SBG ) :IDLE;

(!HOLD & !RFRQ & !LOCK)

:PRE CHG;

:LAN_Off;

( HOLD & !RFRQ & !LOCK)

( HOLD & RFRQ )

:LAN CYC;

ENDCASE;

state PRE CHG : CASE ( RFRQ & !HOLD & !LOCK & SBG ) :IDLE;

(!RFRQ & !LOCK)

:RF CYC:

( RFRQ_ & HOLD)

:LAN CYC;

( RFRQ_ & !HOLD & !LOCK & !SBG_) :PRE_CHG;

ENDCASE;

state LAN OFF : IF (!HOLD) THEN LAN RF

ELSE LAN OFF;

state LAN_RF : IF (RFRQ_) THEN LAN_CYC

ELSE LAN RF;

* ************ Revision History **************

Rev. A 01/03/90 - KKP - First Version

Rev. B 02/20/90 - KKP - Put BG Synchroniziation into PLD.

************************

end ARB

292076-37

```

```

Module CAPORT FLAG '-R3';

Title '82596CA Channel Attention and Port Rev. A 01/03/90

DOCTOR DESIGN, San Diego, CA

PLD20R4-15';

Descrption

*************

FOR: 82596CA / 68030 Interface

" This PLD decodes the 68030 address lines and generates the

Channel Attention and PORT signals to the 82596. The choice

of address is of address is left to the system designer.

" Nine address decode lines are available. They could be

connected to A31-A23. NC1, NC2, NC3, and NC4 are

combinatorial outputs. They can be used as extra address

inputs. NC5 is a standard input that is also available as

an extra address term. If even more decode lines are required,

then the HIADDR input is for the output of the external

decoder. This decode must be done in less than 16 ns.

In the line ADDR = [A09, A08, ....], the values for A09-A01

should be set high or low (inverted) for the desired range.

The decode values for CA_ACC and PORT_ACC (110 and 220) are

arbitrary and can be modified as needed.

SO_ and S1_ are state bits used for generating wait states for

PORT_ assertion.

" UNUSED INPUT PINS

" UNUSED OUTPUT PINS (REGISTERED)

" UNUSED OUTPUT PINS (COMBINATORIAL) : 4

**********************

caport Device 'P20R4';

CLK1_

Pin 1; "I"

VCC

Pin 24;

Pin 2; "I"

HIADDR

Pin 23; "I"

AS

Pin 3; "I"

Pin 22; "I/O"

A01

NC1

Pin 4; "I"

NC2

Pin 21; "I/O"

A02

CA

SO_

Pin 5; "I"

Pin 20; "R, I/O"

A03

A04

Pin

6; "I"

Pin 19; "R,I/O"

A05

7; "I"

S1_

Pin 18; "R, I/O"

Pin

Pin 8; "I"

PORT_

A06

Pin 17; "R, I/O"

A07

Pin 9; "I"

NC3

Pin 16; "I/O"

Pin 10; "I"

80A

Pin 15; "I/O"

NC4

A09

Pin 11; "I"

NC5

Pin 14; "I"

OE_

GND

Pin 12;

Pin 13; "I"

292076-38

```

1

```

"Declarations

x,c = .x.,.c.;

ADDR = [A09, A08, A07, A06, A05, A04, A03, A02, A01, X, X, X]; " User defined address.

CA_ACC MACRO { (ADDR == ^h110) & HIADDR & !AS_ };

PORT_ACC MACRO { (ADDR == ^h220) & HIADDR & !AS_ };

MODE

= [CA, PORT_, SO_, S1_];

= [ 1, 1, 1 , 1 ];

PORT_SET = [ 1, 0, 1 , 1 ]; " Set PORT_ to 82596.

PORT_HLD1 = [ 1, 0, 0 , 1 ]; " Hold for one clock state.

PORT_HLD2 = [ 1, 0, 0 , 0 ]; " Hold for a second clock state.

ACCESS_OFF= [ 1, 1, 0 , 0 ]; " Deassert PORT_ and CA.

CA_SET = [ 0, 1, 1 , 1 ]; " Set CA to 82596.

CA_HLD1 = [0, 1, 0, 1]; "Hold for one clock state.

CA HLD2 = \{0, 1, 0, 0\}; "Hold for a second clock state.

Equations

State_Diagram IN caport MODE

:PORT SET;

state IDLE

: CASE (PORT ACC)

:CA SET;

(CA ACC)

(!(PORT_ACC # CA_ACC)) :IDLE;

ENDCASE;

state PORT_SET : GOTO PORT_HLD1;

state PORT_HLD1 : GOTO PORT_HLD2;

state PORT_HLD2 : GOTO ACCESS_OFF;

state ACCESS_OFF : IF AS_ THEN IDLE

ELSE ACCESS_OFF;

state CA SET : GOTO CA HLD1;

state CA_HLD1

: GOTO CA HLD2;

state CA HLD2 : GOTO ACCESS OFF;

" ******** Revision History *****************

" Rev. A 1/3/90 - KKP - First Version.

** ***********************************

end CAPORT

292076-39

```

```

Module CNVRT FLAG '-R3';

Title '82596CA Signal Conversion

Rev. A

01/03/90

DOCTOR DESIGN, San Diego, CA

PLD20R4-10';

* *************

Descrption

******

FOR: 82596CA / 68030 Interface

This PLD converts the 82596 signals to 68030 type signals.

DELAYAS_ is generated in the RDY PLD to delay AS_ until it is

known whether a multiple or burst transfer is to take place.

A PLD 20R4 was used in this example, requiring seperate

output enables (LANCYC_ and LANCYC2_, connected external to

the PLD) for the registered and latched outputs.

NEWRW_, NEWAS_, NEWDS_, and NEWDBEN_ are registered outputs.

NEWSIZO, NEWSIZ1, NEWAO, and NEWA1 are combinatorial outputs.

All of these signals will be enabled when the 82596 has

control of the local bus, otherwise they will be tri-stated.

The combinatorial outputs are generated using a truth table.

" For completeness, default settings are included for the

impossible BE# input combinations.

UNUSED INPUT PINS

: 3

" UNUSED OUTPUT PINS (REGISTERED)

: 0

UNUSED OUTPUT PINS (COMBINATORIAL) : 0

cnvrt Device 'P20R4';

CLK1_

Pin

1; "I"

VCC

Pin 24;

2; "1"

NC1

Pin

RDY

Pin 23; "I"

3; "I"

DELAYAS_ Pin

NEWA0

Pin 22; "I/O"

BEO_

Pin

4; "I"

NEWSIZO Pin 21; "I/O"

BE1_

Pin 5; "I"

NEWRW_

Pin 20; "R, I/O"

BE2_

NEWAS_

Pin 6; "I"

Pin 19; "R, I/O"

BE3_

Pin 7; "I"

NEWDS

Pin 18; "R, I/O"

WR_

Pin 8; "I"

NEWDBEN_ Pin 17; "R,I/O"

NC2

Pin 9; "I"

NEWSIZ1 Pin 16; "I/O"

NC3

Pin 10; "I"

NEWA1

Pin 15; "I/O"

NEWCBRQ Pin 11; "I"

LANCYC2_ Pin 14; "I"

Pin 12;

LANCYC Pin 13; "I"

292076-40

```

```

Equations

ENABLE NEWAS_ = !LANCYC_;

ENABLE NEWDS_ = !LANCYC_;

ENABLE NEWDBEN_ = !LANCYC_;

ENABLE NEWRW - !LANCYC_;

ENABLE NEWSIZO - !LANCYC2_

ENABLE NEWSIZ1 - !LANCYC2;

ENABLE NEWA0 = !LANCYC2_;

ENABLE NEWA1

= !LANCYC2 ;

!NEWAS_ :=

DELAYAS

" Start after BLAST valid.

# !NEWAS & !NEWCBRQ; " Hold through multiple/burst transfer.

! NEWDS :=

!WR_ & !DELAYAS_ " Start DS_ with AS_ during read cycle.

# WR_ & !NEWDBEN_ & RDY_ " Delay DS_ by 1 clock during a write cycle.

# 'NEWDS & !NEWCBRQ_; " Hold until clock following RDY_ set.

!NEWDBEN :=

DELAYAS

" Enable data transceivers as soon as 82596

begins its cycle.

# !WR & !NEWDBEN & RDY " Hold as long as AS during read.

# WR_ & !NEWDBEN_ & !NEWAS_; " Longer data hold during a write.

!NEWRW_ := WR ;

"invert WR to match processor

" The following truth table converts the byte enable signals from

" the 82596 into the 68030 SIZ signals and address lines AO and

" A1.

Truth_Table

( [BE3_, BE2_, BE1_, BE0_, LANCYC2 ] -> [NEWSIZ1, NEWSIZ0, NEWA1, NEWA0] )

] -> [

[X,X,X,X,

, 1

j -> [

[1,1

, 1 ,

1

1

, 1

] -> [

1 1

, 1 , 0 ,

0

0

1

, 1

, 0

, 0

0

] -> [

[ 1

1

, 0

, 0

, 0

[ 1

0

] <- [

1

1

, 0

0 1

, 0

, 0

0

] -> [

0

, 1

, 0

] -> [

, 1 ,

0

0

1 , 1

, 0

, 0

ο,

0

[ 1

, 1 ,

] -> [

1

, 0

0 1

, 0 , 1 , 0

] -> [

1,

1

[1,0,1,1,0

] -> [ 0

1,

0 , 1 ];

[0,0,1,1,0]->[1,

0 , 0 , 0 ];

[0,1,1,1,

0

] -> [ 0

292076-41

```

```

Module RDY FLAG '-R3';

Title '82596CA Ready and Burst Cycle Logic Rev. A 01/03/90

DOCTOR DESIGN, San Diego, CA

PLD20R4-10';

***************

Descrption

This PLD generates the RDY_ and BRDY_ signals to the 82596.

It also generates the Burst Request (CBREQ_) signal to the

memory controller. It uses the 68030 signals Address Strobe

(AS_), Data Strobe (DS_), Data Bus Enable (DBEN_), Data

Acknowledge (DSACK ) and Synchronous Termination (STERM ). It

also uses Cache Burst Acknowledge (CBACK_) from the memory

controller and Burst Last (BLAST_) from the 82596. The

DELAYAS signal is used to delay the generation of AS to the

memory controller in order to determine whether a burst transfer

is about to take place. Because CLK1 is needed for both the

flip-flop registers and in the combinatorial equations, it

is connected to both pins 1 and 2. Two separate names are

required in the equations (CLK1_ and CCLK1_).

The first three burst data transfers between the 82596 and the

memory will be acknowledged with the BRDY_ signal. The last

(fourth) burst data transfer cycle will be acknowledged with a

RDY_.

This PLD must be 10 ns or faster to meet BRDY set-up to CLK1_

on 82596.

The output DELAYRDY is only used inside this PLD to generate

a delay for the RDY_ signal to the 82596.

UNUSED INPUT PINS

UNUSED OUTPUT PINS (REGISTERED)

UNUSED OUTPUT PINS (COMBINATORIAL) : 1

**************

rdy Device 'P20R4';

1; "1"

CLK1

Pin

VCC

Pin 24;

CCLK1

Pin

2; "1"

NC2

Pin 23; "I"

AS_

Pin

3; "I"

RDY

Pin 22; "I/O"

4; "I"

Pin

Pin 21; "I/O"

DS

5; "I"

STERM

DELAYAS_ Pin 20; "R,I/O"

Pin

DBEN_

Pin 6; "I"

S0

Pin 19; "R, I/O"

NEWCBREQ_ Pin 18; "R,I/O"

ADS

Pin 7: "I"

CBACK_

Pin 8; "I"

Pin 17; "R, I/O"

NC3

Pin

9; "I"

NC1

DELAYRDY_ Pin 16; "I/O"

Pin 10; "I"

DSACK

NC4

Pin 15; "I/O"

Pin 11; "I"

BLAST

LANCYC_

Pin 14; "I"

Pin 12;

GND

OE_

Pin 13; "I"

```

```

"Declarations

= [DELAYAS_, SO, NEWCBREQ_];

MODE

- [1,1,1];

BLST WT = [0,1,1]; " Wait for BLAST to determine if burst data transfer.

NO_BURST = [1,0,1]; "BLAST_ active so no burst transfer.

BRST_CYC = [0,0,1]; "BLAST_ not active so multiple or burst transfer.

STERM_1 = [0,0,0]; "Wait for acknowledge.

STERM_2 = [0,1,0]; "Wait for acknowledge.

STERM_3 = [1,1,0]; " Wait for acknowledge.

Equations

!RDY_ = !BLAST_ & !DELAYRDY_ & CCLK1_ & !AS_ & CBACK_

" Return RDY_ whenever BLAST_ asserted.

# !STERM & NEWCBREQ

" Fourth burst transfer or synchronous transfer.

# !RDY & !DBEN_;

" Hold RDY until data requirement met.

!BRDY = !STERM & !NEWCBREQ_ & !CBACK |

" Assert BRDY_ during burst cycles

# !BRDY & !CCLK1_;

" Hold so recognized on rising edge of CLK1 to 82596.

!DELAYRDY_ =

!DS_ & !LANCYC_ & !CCLK1_ " Delay RDY for data setup.

" Hold until end of data cycle.

# !DELAYRDY & !AS ;

State Diagram IN rdy MODE

: IF !ADS_ THEN BLST WT

state IDLE

ELSE IDLE;

state BLST_WT : IF !BLAST_ THEN NO_BURST

ELSE BRST CYC;

state NO BURST : GOTO IDLE;

state BRST_CYC : CASE (!BRDY_ & !CBACK_) : STERM ((!BRDY_ & CBACK_) # !BLAST_) : IDLE;

: STERM 1;

(BRDY_ & BLAST_)

: BRST CYC;

ENDCASE;

state STERM_1 : CASE (!BRDY_ & !CBACK_)

: STERM 2;

((!BRDY_ & CBACK_) # !BLAST_) : IDLE;

(BRDY & BLAST )

: STERM 1;

ENDCASE:

292076-44

```

1